## The Real-Time Data Analysis and Decision System for Particle Flux Detection in the LHC Accelerator at CERN.

by Christos Zamantzas

A thesis submitted for the degree of

Doctor of Philosophy

in Electrical and Electronic Engineering

School of Engineering and Design Brunel University

January 2006

#### **Abstract**

The superconducting Large Hadron Collider (LHC) under construction at the European Organisation for Nuclear Research (CERN) is an accelerator unprecedented in terms of beam energy, particle production rate and also in the potential of self-destruction. Its operation requires a large variety of instrumentation, not only for the control of the beams, but also for the protection of the complex hardware systems.

The Beam Loss Monitoring (BLM) system has to prevent the superconducting magnets from becoming normal conducting and protect the machine components against damages making it one of the most critical elements for the protection of the LHC.

For its operation, the system requires 3600 detectors to be placed at various locations around the 27 km ring. The measurement system is sub-divided to the tunnel electronics, which are responsible for acquiring, digitising and transmitting the data, and the surface electronics, which receive the data via 2 km optical data links, process, analyze, store and issue warning and abort triggers. At the surface installation, the processing units (BLMTCs) include Field Programmable Gate Array (FPGA) devices. Each FPGA is treating the beam loss signals collected with a rate of 25 kHz from 16 detectors. It calculates and maintains 192 moving sum windows, giving loss duration integrations of up to the last 84 seconds. For the generation of the abort triggers, demanding the extraction of the circulating beams, it compares the moving sums calculated with threshold values chosen for the given beam energy. Those thresholds can be uniquely programmable for each detector allowing calibration and offset factors to be included.

In this thesis, the BLMTC's design is explored giving emphasis to the methods followed in providing very reliable physical and data link communication layers, in merging the data from a Current-to-Frequency converter and an ADC into one value, and in keeping the moving sums updated in a way that gives the best compromise between memory needs, computation, and approximation error.

## **Table of Contents**

| ABSTRAC          | Γ                                                                    | I        |

|------------------|----------------------------------------------------------------------|----------|

| ACKNOWI          | LEDGEMENTS                                                           | VI       |

| INTRODU          | CTION                                                                | 1        |

| CHAPTER          | 1. THE LARGE HADRON COLLIDER AT CERN                                 |          |

|                  | IE ACCELERATOR CHAIN                                                 |          |

|                  | IC Machine Operation                                                 |          |

| 1.2.1            | Filling                                                              |          |

| 1.2.2            | Acceleration and Squeeze                                             |          |

| 1.2.3            | Collision                                                            | 8        |

| 1.3 LH           | IC CHALLENGES IN ACCELERATOR PHYSICS                                 | 9        |

| 1.3.1            | The beam-beam effect and Beam Loss                                   |          |

| 1.3.2            | Particles have to remain stable for long times                       |          |

| 1.3.3            | Beam Losses and Quench of Magnets                                    |          |

|                  | IC Machine Protection                                                |          |

| 1.4.1            | Beam Loss Monitoring System (BLM)                                    |          |

| 1.4.2            | Beam Energy Tracking System (BETS)  Beam Interlock System (BIS)      |          |

| 1.4.3            |                                                                      |          |

| KEFERENC         | CES                                                                  | 18       |

| CHAPTER          | 2. BEAM LOSS MONITORING SYSTEM FOR THE LHC                           | 21       |

| 2.1 BE           | EAM LOSS DETECTORS                                                   | 22       |

| 2.2 FR           | ONT-END ELECTRONICS                                                  | 24       |

| 2.2.1            | The BLMCFC Card                                                      | 24       |

| 2.2.2            | 1 5                                                                  |          |

| 2.2.3            | Front-End FPGA Processes                                             |          |

| 2.3 OF           | PTICAL FIBRES                                                        | 31       |

| 2.4 Sid          | GNAL RECEPTION AND PROCESSING ELECTRONICS                            | 32       |

|                  | The DAB64x Card                                                      |          |

| 2.4.2            | The BLM Mezzanine Card                                               |          |

| 2.4.3            | Surface FPGA Processes                                               |          |

|                  | JTPUT SIGNAL CONCENTRATION                                           |          |

| 2.6 TH           | IE BACK-END CRATES                                                   | 39       |

| 2.7 RE           | ELIABILITY AND AVAILABILITY ENHANCEMENT                              |          |

| 2.7.1            | Tunnel System                                                        |          |

| 2.7.2            | Surface System                                                       |          |

|                  | MULATION AND HARDWARE VERIFICATION TOOLS                             |          |

| 2.8.1            | Static Timing Analysis                                               |          |

| 2.8.2            | Simulation Tests                                                     |          |

| 2.8.3<br>2.8.4   | SignalTap II Logic Analysis In-System Updating of Memory & Constants |          |

| Z.0.4  RECEDENCE |                                                                      | 44<br>14 |

| CHAP'      | TER 3. DATA TRANSMISSION                           | 48 |

|------------|----------------------------------------------------|----|

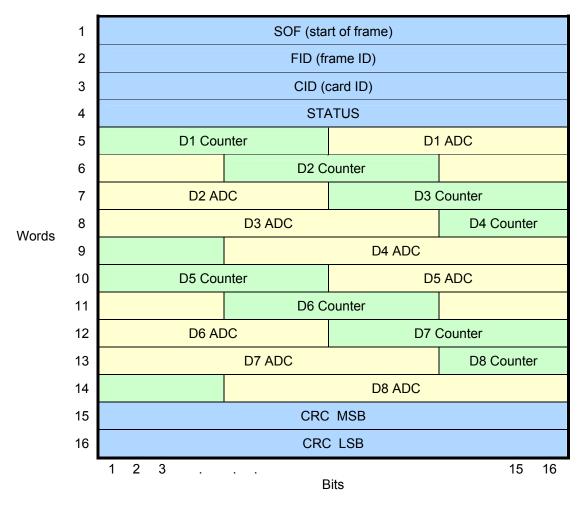

| 3.1        | THE BLM DATA PACKET                                | 49 |

| 3.1        | 1.1 Formatting of the BLM Packet                   | 51 |

| 3.2        | PHYSICAL COMPONENTS                                | 52 |

| 3.2        | 2.1 The GOL (Gigabit Optical Link)                 | 52 |

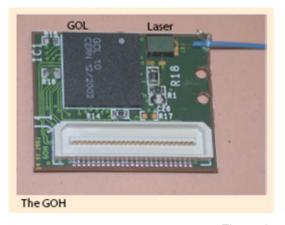

|            | The GOH (Gigabit Opto-Hybrid) Configuration        |    |

|            | 2.3 The TLK Transceiver                            |    |

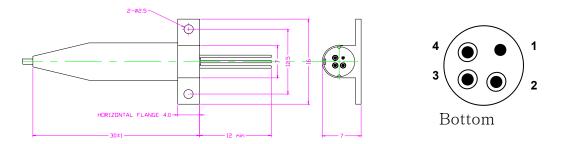

|            | The NTPPT-3 Photodiode                             |    |

|            | 2.5 The Non-Volatile Memory                        |    |

| 3.3        |                                                    |    |

| 3.4        |                                                    |    |

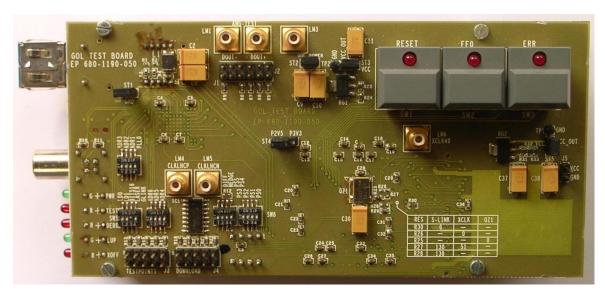

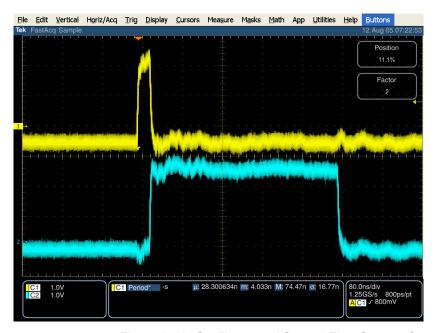

|            | 4.1 Using the GOL Test Board                       |    |

|            | 4.2 Using the CFC Card                             |    |

| 3.5        |                                                    |    |

| Refe       | RENCES                                             | 64 |

| CHAP'      | TER 4. DATA RECEPTION & ERROR DETECTION            | 67 |

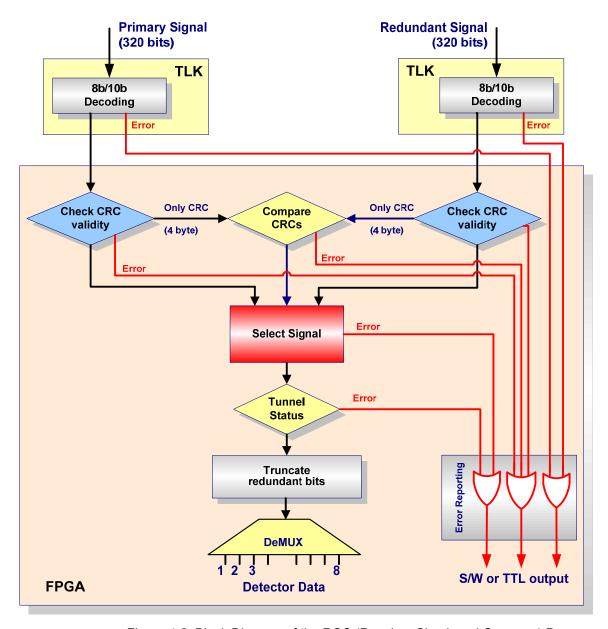

| 4.1        | RELIABILITY INCREASE OF LINK                       | 68 |

| 4.1        | 1.1 Redundant Signal Assessment                    | 68 |

| 4.1        | 1.2 Evaluation of Comparison Scenarios             | 68 |

| 4.2        | THE RCC (RECEIVE, CHECK AND COMPARE) PROCESS       | 70 |

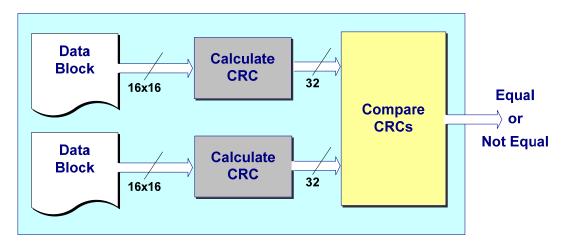

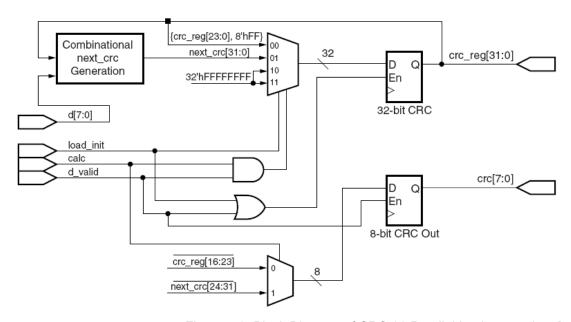

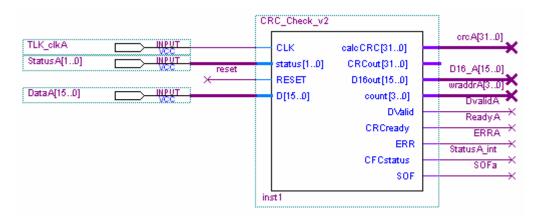

| 4.3        | CRC CODING                                         | 72 |

| 4.3        |                                                    |    |

|            | Probability of CRC Errors Non-Detection            |    |

|            | 3.3 CRC Parallel Implementation                    |    |

|            | 3.4 CRC VHDL Implementation                        |    |

| 4.4        |                                                    |    |

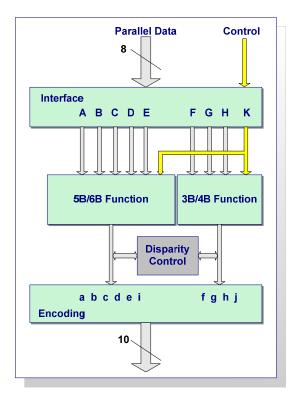

|            | 4.1 Encoding algorithm                             |    |

|            | 4.2 Decoding algorithm                             |    |

| •••        | 4.4 Error checking using redundancy of 8B/10B code |    |

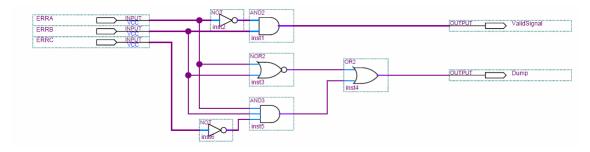

| 4.5        | COMBINED ERROR DETECTION OF CRC AND 8B/10B CODE    |    |

| 4.6        | SELECTION OF SIGNAL                                |    |

| 4.0<br>4.6 |                                                    |    |

|            | 5.2 Implementation of the Signal Select Function   |    |

| 4.7        | METASTABILITY FROM CLOCK DOMAIN CROSSING           |    |

| 4.8        | IMPLEMENTATION OF THE RCC PROCESS                  |    |

|            | 8.1 Resource Utilisation by the RCC Process        |    |

| 4.9        | STATIC TIMING SIMULATION OF THE RCC PROCESS        |    |

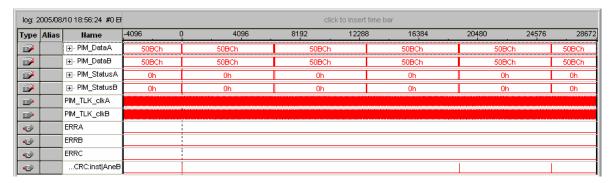

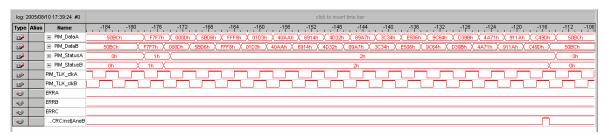

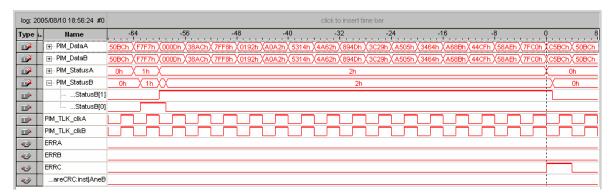

| 4.10       | HARDWARE VERIFICATION TEST OF THE RCC PROCESS      |    |

| 4.11       | SUMMARY                                            |    |

|            | SUMMARY                                            | 92 |

|            |                                                    |    |

| CHAP' | TER 5. DATA ACQUISITION & MERGING ALGORITHM            | 96  |

|-------|--------------------------------------------------------|-----|

| 5.1   | DATA ACQUISITION                                       | 96  |

| 5.2   | DATA MERGING ALGORITHM                                 | 98  |

| 5.2   | 2.1 Positive Difference Result                         |     |

| 5.2   | 2.2 Negative Difference Result                         | 99  |

| 5.3   |                                                        |     |

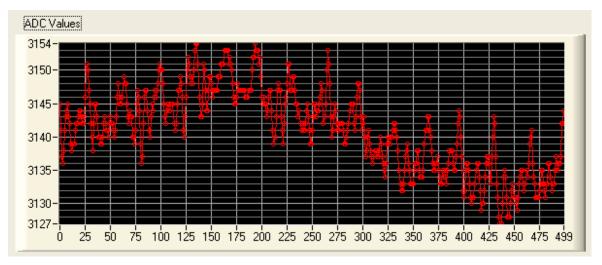

|       | 3.1 Visualisation of the Noise Pattern                 |     |

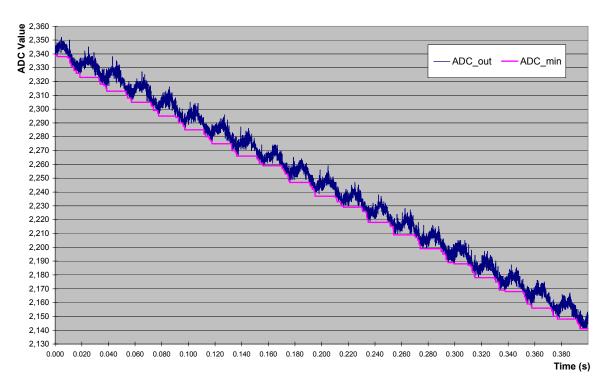

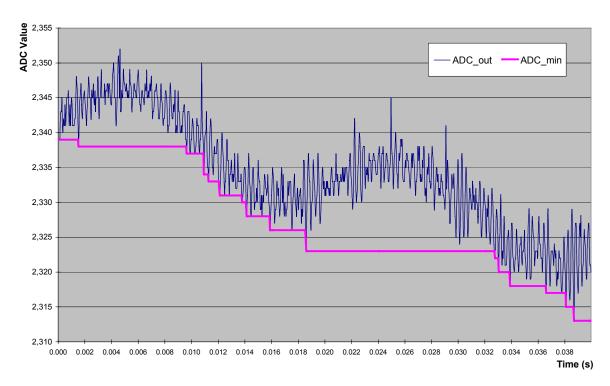

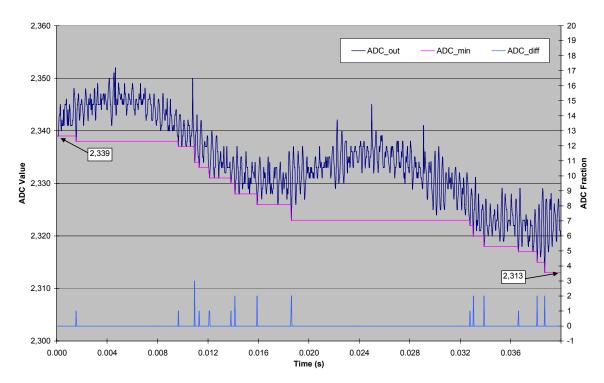

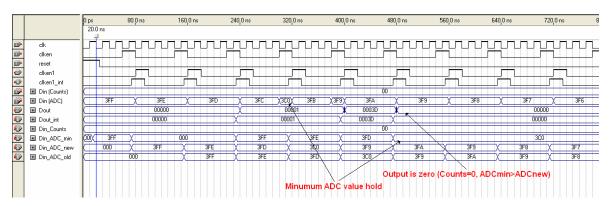

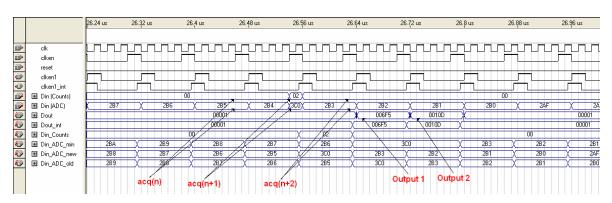

|       | 3.2 Minimum-Value-Hold Function                        |     |

|       | 3.3 Data-Combine Process Expected Outputs              |     |

| 5.4   | SYSTEMATIC ERROR DUE TO THE DATA-COMBINE PROCESS       |     |

| 5.5   | IMPLEMENTATION OF THE DATA-COMBINE PROCESS             |     |

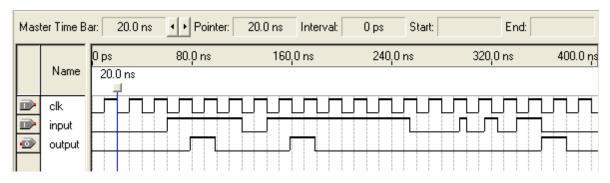

| 5.6   | STATIC TIMING SIMULATION OF THE DATA-COMBINE PROCESS   |     |

| 5.7   | HARDWARE VERIFICATION TEST OF THE DATA-COMBINE PROCESS | 110 |

| 5.8   | Summary                                                | 112 |

| Refe  | ERENCES                                                | 113 |

| CHAD' | TER 6. REAL-TIME DATA PROCESSING                       | 115 |

|       | CHOICE OF DATA PROCESSING METHOD                       |     |

| 6.1   |                                                        |     |

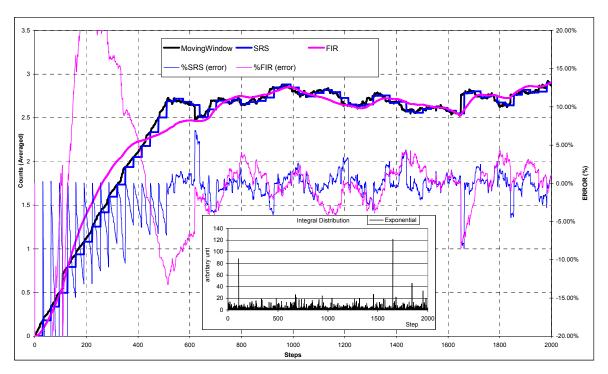

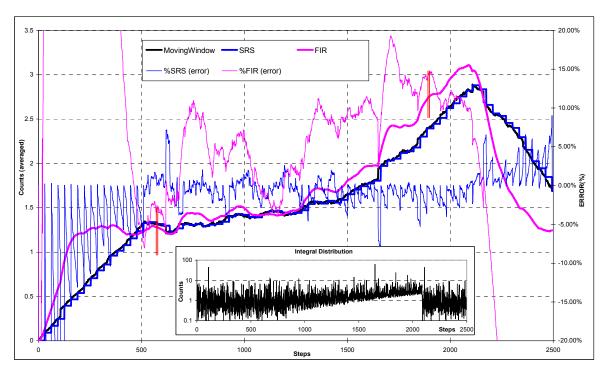

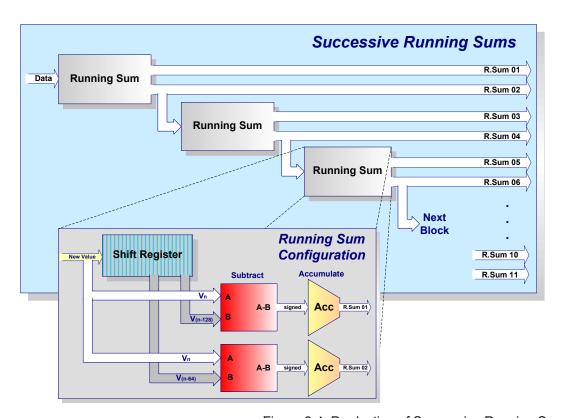

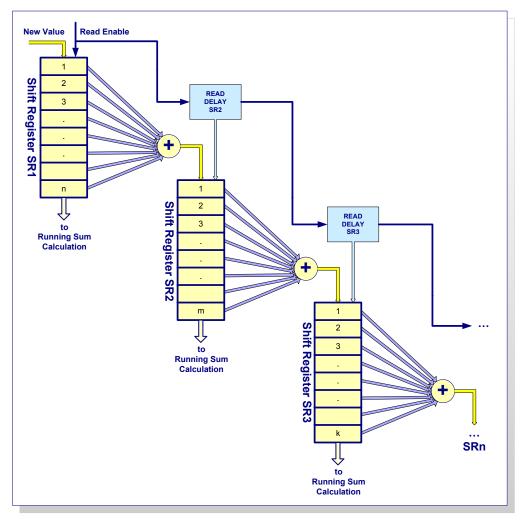

| 6.2   | SUCCESSIVE RUNNING SUM (SRS) DATA PROCESSING           |     |

|       | 2.1 Running Sums                                       | 120 |

| 6.3   |                                                        |     |

|       |                                                        |     |

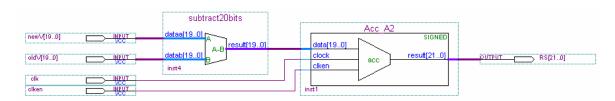

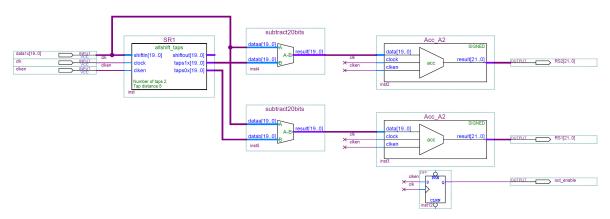

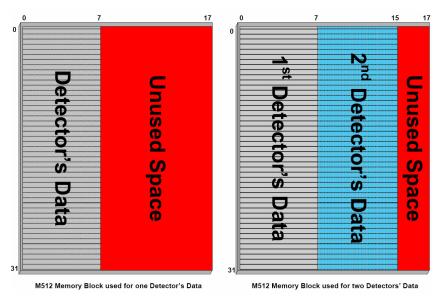

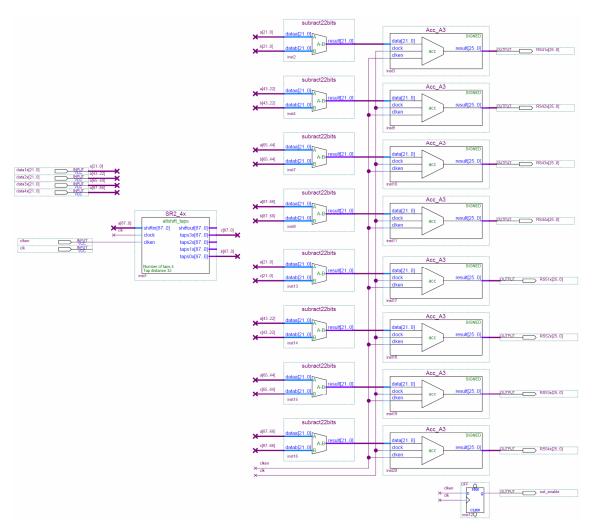

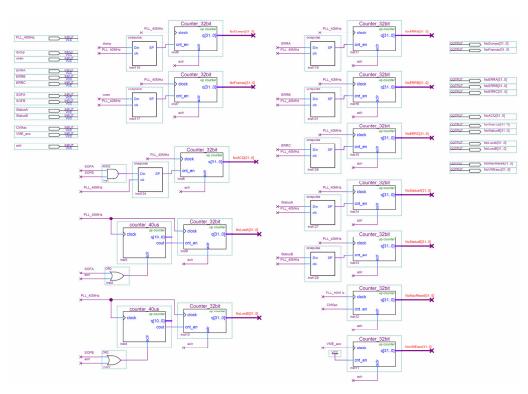

| 6.4   | IMPLEMENTATION OF THE SRS                              |     |

|       | 4.2 Production and Maintenance of a Running Sum        |     |

|       | 4.3 Optimisations of the Running Sums                  |     |

|       | 4.4 Successive Running Sums in the BLMTC               | 128 |

| 6.5   |                                                        |     |

| 6.6   | HARDWARE VERIFICATION OF THE SRS PROCESS               |     |

| 6.7   | SUMMARY                                                |     |

|       | ERENCES                                                |     |

|       | TER 7. THRESHOLD COMPARATOR & CHANNEL MASKING          |     |

|       |                                                        |     |

| 7.1   | THRESHOLD LEVEL COMPARATOR (TC)                        |     |

| 7.    |                                                        |     |

| · ·-  | 2.1 Masking Table                                      |     |

| 7.3   |                                                        |     |

|       | 3.1 Optimisation of the TC Process                     |     |

|       | 3.2 Resource Utilisation by the TC Process             |     |

| 7.4   | IMPLEMENTATION OF THE THRESHOLD TABLE                  |     |

|       | 4.1 Memory Requirements for the Threshold Table        |     |

|       | 4.2 The Th-Table Function                              |     |

| 7.4   | 4.3 Resource Utilisation by the Threshold Table        | 149 |

| 7.5   | IMPLEMENTATION OF THE MASKING PROCESS                  | 150 |

| 7.     | 5.1 Resource Utilisation by the Masking Process       | 152 |

|--------|-------------------------------------------------------|-----|

| 7.6    | SUMMARY                                               | 153 |

| Refi   | ERENCES                                               | 155 |

| СНАР   | TER 8. DATA LOGGING & POST-MORTEM RECORDING           | 157 |

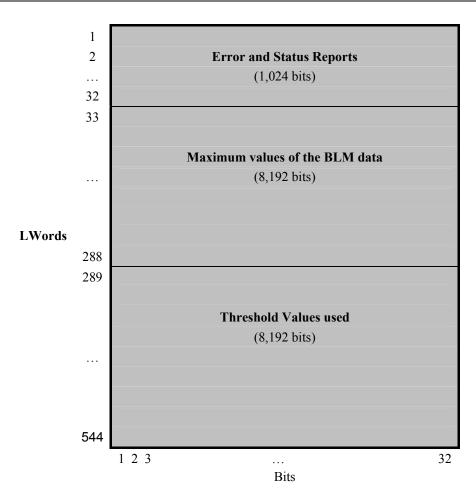

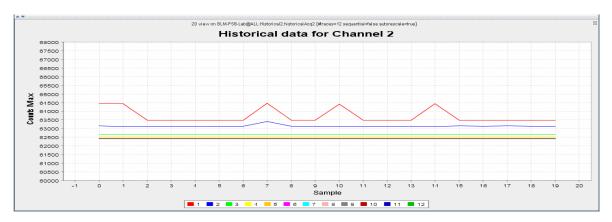

| 8.1    | Data Logging                                          | 159 |

| 8.2    | Post Mortem Recording                                 | 161 |

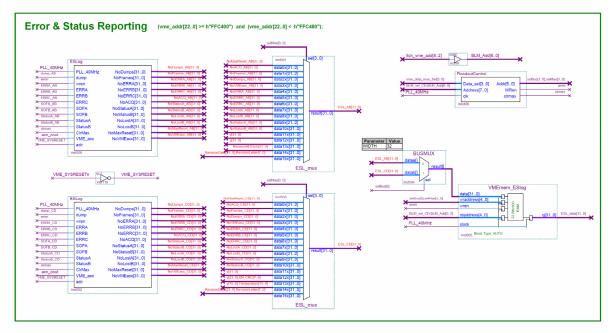

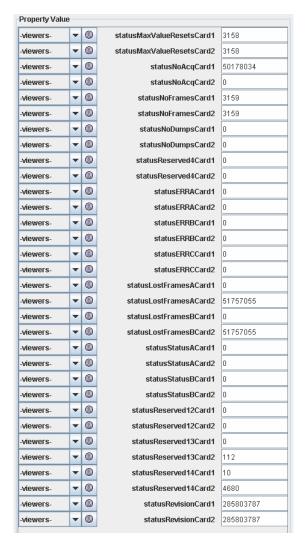

| 8.3    | IMPLEMENTATION OF THE ERROR AND STATUS REPORTING      | 162 |

| 8.     | 3.1 The ESLog Function                                |     |

|        | 3.2 Error and Status Reporting (ESR) in the BLMTC     |     |

|        | 3.3 Resource Utilisation by the ESR Process           |     |

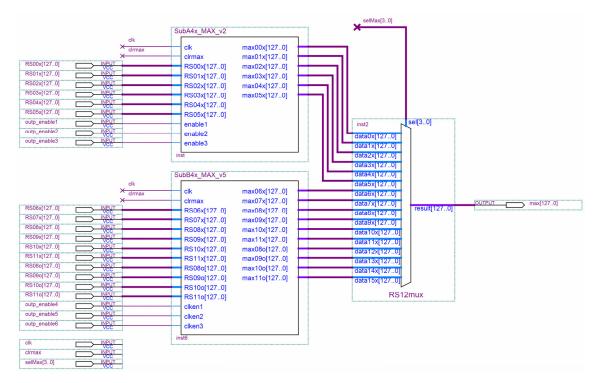

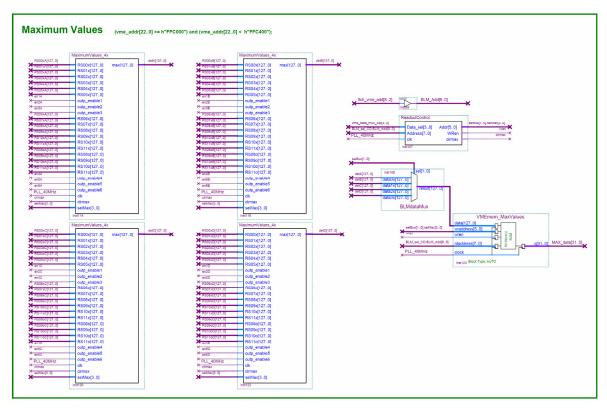

| 8.4    | IMPLEMENTATION OF THE MAXIMUM VALUES LOGGING          |     |

|        | 4.1 Maximum Value Calculation                         |     |

|        | 4.3 Resource Utilisation by the Maximum Value prosess |     |

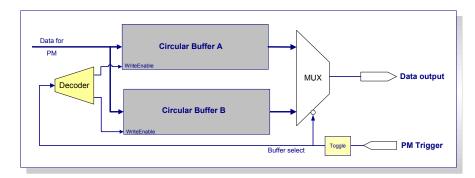

| 8.5    | IMPLEMENTATION OF THE POST MORTEM                     |     |

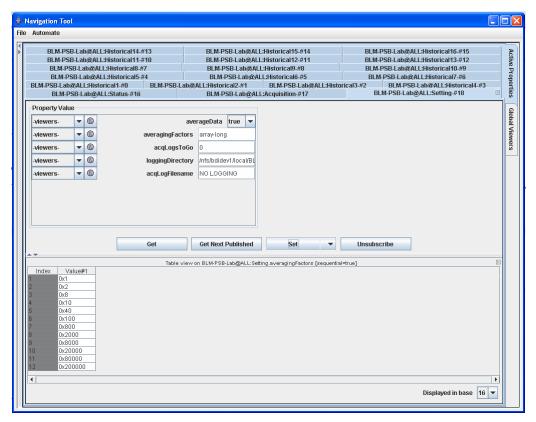

| 8.6    | Data Logging User Interface                           |     |

| 8.7    | Summary                                               |     |

|        | ERENCES                                               |     |

| CONC   | A HOLONG                                              | 100 |

| CONC   | LUSIONS                                               | 180 |

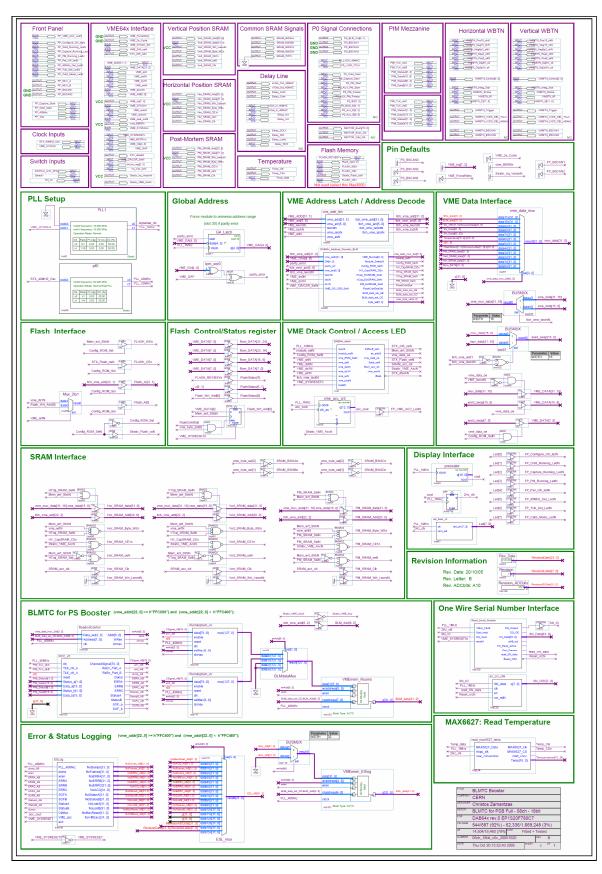

| APPE   | NDIX A. IMPLEMENTATION OF THE BLMTC                   | 185 |

| A.1    |                                                       |     |

| A      | .1.1 VHDL Code for CRC Check                          |     |

| A.2    | DEGIGNATED ONL DATE COMBINED I ROCEDS                 |     |

|        | 2.1 VHDL Code for Data-Combine                        |     |

|        | DESIGN REPORT – MASKING PROCESS                       |     |

|        | .3.1 VHDL Code for the Inhibit Function               |     |

|        | DESIGN REPORT –LOGGING PROCESS                        |     |

|        | 4.2 VHDL Code for Calculating the Maximum Value       |     |

|        | _                                                     |     |

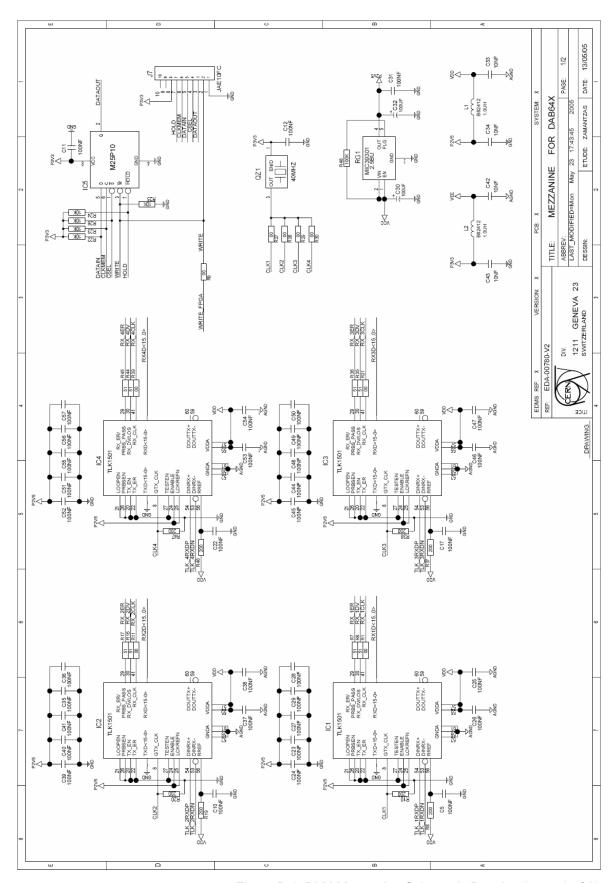

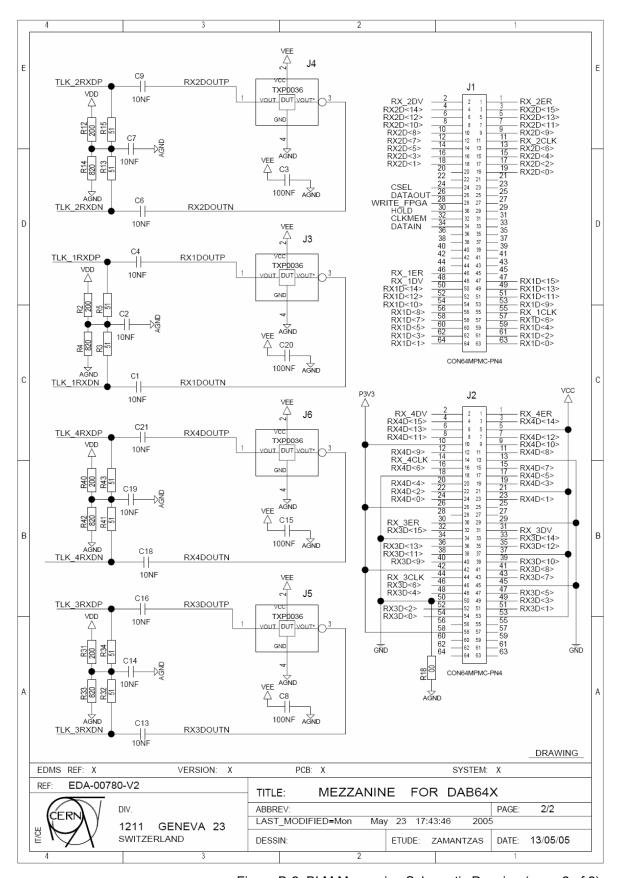

| APPE   | NDIX B. BLM MEZZANINE SCHEMATIC DRAWINGS              | 194 |

| APPE   | NDIX C. BLMTC VERSIONS                                | 196 |

| C.1    | BLMTC FOR THE PS BOOSTER AT CERN                      | 197 |

| C.2    | BLMTC FOR THE HERA AT DESY                            | 200 |

| APPE   | NDIX D. LINEARITY TEST OF THE BLM SYSTEM              | 202 |

| LIST ( | OF FIGURES                                            | 203 |

| LIST ( | OF TABLES                                             | 207 |

| LIST ( | OF ACRONYMS                                           | 209 |

PhD Thesis vi

### **Acknowledgements**

I wish to express my gratitude to all the people who have contributed to the completion of this thesis with their knowledge, encouragement and by making my stay at CERN that enjoyable. The following people are only some of those whose help was invaluable.

I would like to start with Cinzia Da Via and Bernd Dehning, not only because they trusted me with this very important task but also for their help to accomplish it. I was still an undergraduate when Cinzia became my supervisor at Brunel University. In this function, for the last six years she led my studies. Between other, she introduced me to CERN, an institute at the time unknown to me. Bernd, my supervisor at CERN and leader of the Beam Loss section, welcomed me and introduced me in this community. He gave me my first accelerator physics knowledge, and found the funds to allow me to attend many courses and conferences. His exceptional character is always an example to follow. Both Cinzia and Bernd deserve my eternal gratitude for believing in me, treating me as equal, but mostly for allowing me to grow in a much better person. From Brunel, I would like also to thank Stephen Watts, my second university supervisor, for arranging all matters with the university and hence providing me with this opportunity.

Just as no research and development can be done in one day, no product can be produced in a vacuum. There are a number of people I would like to acknowledge for their contribution in this project. Starting with Gianfranco Ferioli, our chief engineer, always ready to share his immense knowledge and experience in electronics and accelerators. Ewald Effinger and Jonathan Emery, my companions in crime, whose help allowed me to reach many goals. They relieved me from any other tasks in the last couple of months to allow me to prepare my thesis undisturbed. Gianluca Guaglio, the source of reliability, pushed and helped to provide a much better design. Claudine Chery who created the prototypes, and the rest of the BL section, that is Stian Erlend Sundsoy Forde, Michael Hodgson, Eva Barbara Holzer, Jan Koopman. Daniel Kramer, Roman Leitner, Laurette Ponce, Virginia Prieto, Helge Haakon Refsum, Ion Savu, Markus Stockner, and Raymond Tissier, for their support and for making a really nice working environment.

Others have also contributed in this work without being directly involved in this project. I would like to recognise Paulo Moreira, from the Microelectronics group, for providing his test-bench and for his time and effort to pass me his valuable insights into many of the issues on the GOL device. Jean-Marc Combe, from the DEM group, for the help and his proposals in the layout of the BLM Mezzanine card. Daryl Bishop, from TRIUMF, even though being in the other side of the Atlantic he was always available to discuss and provide solutions on the DAB card. Graham Waters, also from TRIUMF, for providing an interface for flashing my code over the VME. Jose Luis Gonzalez for making possible the production of this card's last minute modifications for our system. Stephen Jackson for his ideas and the construction of the Navigator. Subroto Datta, from Altera, for his support with the Quartus II software. Ray Andraka for his help, through the FPGA newsgroup, in the DSP techniques and for introducing me to the CIC filters. Paschalis Vichoudis, always available to discuss current trends in the digital design domain. Sotiris Vlachos for providing corrections and the much-needed moral support during the writing process.

Without friends life would be so empty. For filling this gap, I would like to thank Federico Roncarolo, for being my first friend at CERN and introducing me to the most interesting group of people. Too many to list but so warm that welcomed me in their houses from the first day, as if I was an old friend. Boris Bellesia, for wasting many of his weekends to teach me the art of snowboarding. Antonio Vergara for passing to me the best apartment in Geneva and Christos Sagianos for offering help with the deposit and the furniture. Of course, I would never omit the Super Trois Genève, the funniest group of people, whose stories of lost chicken have become epic.

Finally, this cannot be dedicated to any other than Elena and the rest of my family for making my life full, for putting up with my mumblings and sketches all over the house, and for their unconditional love, eternal support and inspiration all these years...Love always.

PhD Thesis VIII

#### Introduction

The Large Hadron Collider (LHC) is the next circular accelerator being constructed at the European Organisation for Nuclear Research (CERN). It will provide head-on collisions of protons at a centre of mass energy of 14 TeV for high energy particle physics research. The LHC is currently being installed in the 27 km long LEP tunnel. In order to reach the required magnetic field strengths, superconducting magnets cooled with superfluid helium will be installed.

The energy stored in the LHC can potentially damage many elements of the accelerator or could make its operation very inefficient. The 10 GJ stored in the magnetic fields of the magnets needs a protection system to dissipate the energy in case of the transition of the electrical conductors from the superconducting to the normal conducting state (quench). Moreover the 700 MJ stored in the circulating beams could initiate quenches or cause damages if only a very small fraction of the circulating beam particles deposit their energy in the equipment. The consequence will be either the warming up of the magnet coil, causing a downtime of several hours necessary for cooling down again the magnet to reach the superconducting state, or a repair time of months in the case of equipment damage. This thesis has been developed inside the CERN team responsible for the machine protection and more specifically in its section assigned to provide to the LHC a protection process from the beam losses. Thus, a system has been implemented for measuring continuously such losses and acting when those exceed specified thresholds.

The thesis begins with a general introduction to the aim and the specifications of the LHC, as well as the objectives and important parts of the machine protection system. The task, as described in Chapter 2, of observing continuously the particle losses and signalling the safe extraction of the circulating beam before the losses reach the quench level is accomplished by the Beam Loss Monitoring (BLM) system. The monitors are formed by ionization chambers that produce an electric current proportional to the particle rate traversing their volume. It is measured by an analogue front-end, which is located near those detectors in the LHC tunnel and has to cover a dynamic range of nearly nine orders of magnitude.

The second part of this thesis, which marks the beginning of the work done by the author, is committed to the effort to provide very reliable implementations of the physical and data link layers for the BLM system. Because of the radiation environment in the tunnel, the evaluation of the detector signal has to be performed in the surface buildings. This leads to long transmission distances of up to 2 km between the front-end in the tunnel and the processing module on the surface. In Chapter 3, the optical link construction is shown together with the data arrangement in a packet. The link operates in the gigabit region to provide low system latency and it is using radiation tolerant devices for the parts residing in the tunnel installation. A significant portion of the data packet is occupied with extra information, to be used at the far end of the link by the processing module, for monitoring the correct operation of the tunnel installation. This reception process, facilitated in the entry stage of the surface FPGA, is shown in Chapter 4. In addition, its implementation has been done in a way that ensures the correct reception and detection of erroneous transmissions by using digital techniques like the Cyclic Redundancy Check (CRC) and the 8B/10B algorithms.

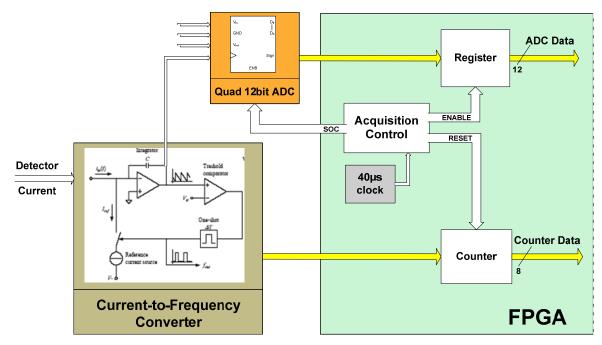

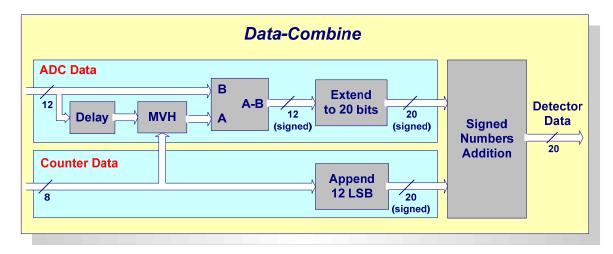

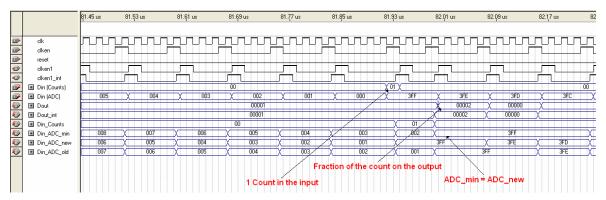

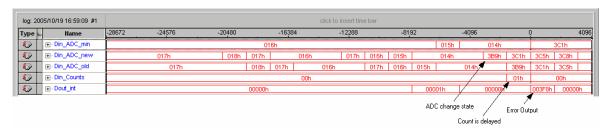

The third part is dedicated to the real-time processing of the data. In order to extend the dynamic range of the system the digitisation of the detector signal is done by a Current-to-Frequency converter (CFC) together with an ADC. The two types of data acquired for each detector signal with those digitisation methods are different and pre-processing is needed in order for those to be merged into one value. More specifically, the measurement of the pulses, produced by the CFC, using a counter relates to the average current induced from the previous acquisition. On the other hand, the voltage measured by the ADC is the fraction of the charge in the capacitor. Chapter 5 investigates and proposes a merging method of those two different types of data, as well as it sets an acquisition strategy that provides accuracy and avoids errors. Consecutively, the BLM data main processing requires analysis of the signal pattern in time. Given the tolerance acceptable for quench prevention by the specifications, the quench thresholds versus loss duration curves have been approximated with a minimum of steps fulfilling the tolerance. In this way, the number of sliding integration windows has been reduced to twelve. Chapter 6 shows how this was made possible and proposes a highly efficient strategy of keeping many moving windows that can span to long integration time periods for each detector data.

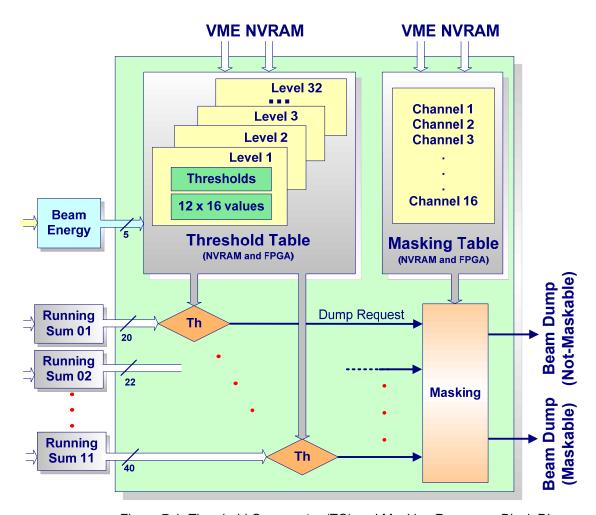

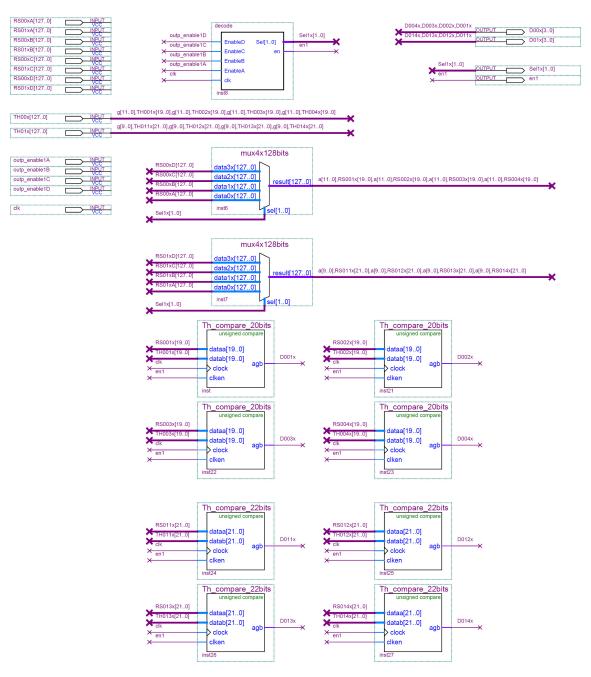

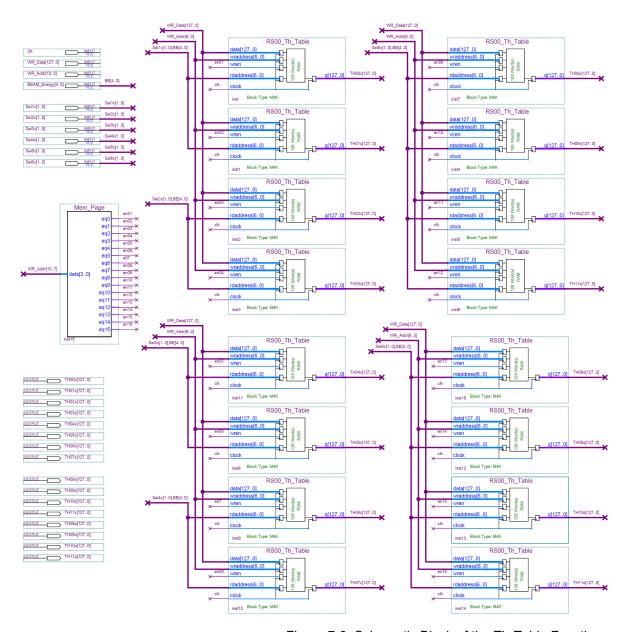

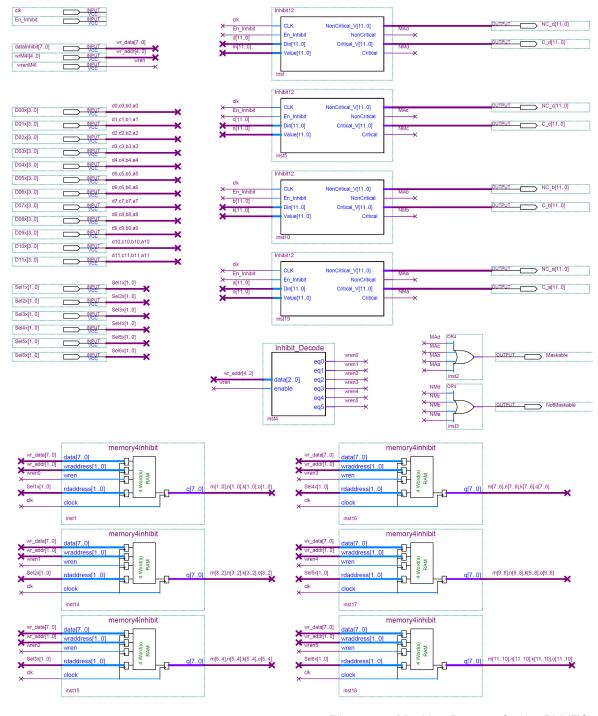

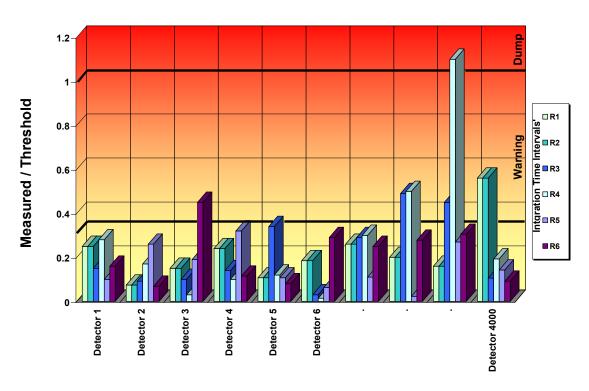

The forth and final part, of this thesis, discusses the processes reaching to the output stages. Every Running Sum, after every new calculation, needs to be compared with its corresponding threshold value that was chosen by the beam energy reading given that moment. If the level is found to be higher, the comparator will initiate the necessary dump request. Chapter 7 proposes an implementation of a quench level Threshold Comparator that allows also the possibility of channel masking. It is using unique tables for each detector that provide the threshold values depending on the beam energy reading. Finally, Chapter 8 shows the concentration of the data for the Control Room. The main purpose of the Logging System is to continuously record and provide an online display to the Control Room of the machine status and show slow or infrequent changes. The BLM system will contribute by providing the loss rates, normalised with respect to the quench levels so that abnormal or higher local rates could thereby be spotted easily.

In the appendixes, the reader can find important parts of the VHDL code used in the construction of the FPGA firmware, the schematics of the BLM Mezzanine card, information on two similar configurations of the BLMTC used for measurements in available accelerators, and the results of a linearity test made on those systems.

# 01

The Large Hadron Collider at CERN

## **Chapter 1. The Large Hadron Collider at CERN**

CERN is the European Organization for Nuclear Research, the world's most influential particle physics centre. Founded in 1954, the laboratory was one of Europe's first joint ventures, and is an example of international collaboration. From the original 12 signatories of the CERN convention, membership has grown to the present 20 Member States. The laboratory sits astride the Franco-Swiss border west of Geneva at the foot of the Jura mountains.

Its research programme attracts scientists not only from the Member States but literally worldwide. Some 6500 scientists, half of the world's particle physicists, use the available facilities. They represent 500 universities and over 80 nationalities.

CERN's primary function is to provide research facilities and basic support to this community of users. By accelerating particles to very high energies and smashing them into targets or into each other, the forces acting between them can be unravelled. CERN's accelerators are amongst the world's largest and most complex scientific instruments.

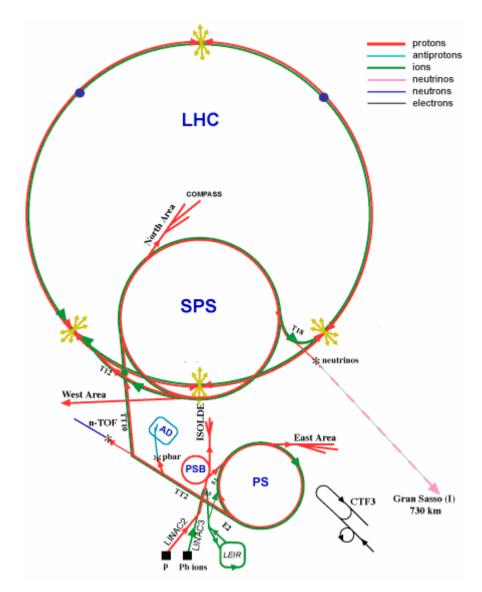

#### 1.1 THE ACCELERATOR CHAIN

The accelerator chain at CERN is a succession of machines with increasingly higher energies, injecting the beam each time into the next one, which takes over to bring the beam to an energy even higher, and so on. The flagship of the complex will be the Large Hadron Collider (LHC).

CERN's accelerator complex (see Figure 1-1) is the most versatile in the world. It includes particle accelerators and colliders, can handle beams of electrons, positrons, protons, antiprotons, and "heavy ions" (the nuclei of atoms, such as oxygen, sulphur, and lead). Each type of particle is produced in a different way, but then passes through a similar succession of acceleration stages, moving from one machine to another. The first steps are usually provided by linear accelerators, followed by larger circular machines.

Figure 1-1: The CERN Accelerator Chain. [1]

CERN's first operating accelerator, the Synchro-Cyclotron, was built in 1954, in parallel with the Proton Synchrotron (PS). The PS is today the backbone of CERN's particle beam factory, feeding other accelerators with different types of particles. The 1970s saw the construction of the SPS, at which Nobel-prize winning work was done in the 1980s. The SPS continues to provide beams for experiments and was also the final link in the chain of accelerators providing beams for the LEP machine. It will do also the same for the next big machine, due to start operating in 2007, the LHC.

#### 1.2 LHC MACHINE OPERATION

The LHC will consist of two "colliding" synchrotrons installed in the 27 km LEP tunnel. They will be filled with protons delivered from the SPS and its pre-accelerators at 0.45 TeV. Two superconducting magnetic channels will accelerate the protons to 7-on-7 TeV, after which the beams will counter-rotate for several hours, colliding inside the experimental detectors, until they become so degraded that the machine will have to be emptied and refilled.

#### 1.2.1 FILLING

The first stage in the machine operation is the filling. It begins with the extraction process from the SPS, the transfer of the beam through the transfer lines, the injection into the LHC, and the establishment of captured circulating beam. The filling is done by transferring from the SPS to the LHC bunches of particles. Each bunch contains about 1.1 x 10<sup>11</sup> protons and 2808 of these bunches are transferred during each extraction process. There are mainly three types of equipment involved: the fast kicker magnets (extraction, injection), the acceleration equipment (RF), and the magnetic elements (extraction bumpers in the SPS, transfer-line magnets and the LHC magnets).

#### 1.2.2 ACCELERATION AND SQUEEZE

In the acceleration process, all beam control systems have to start synchronously the execution of the energy ramp. Once the ramp start signal is given, these systems have to maintain the same pace to step through the pre-programmed ramp functions. The synchronisation is provided by the slow timing system: a common start ramp event will be used to trigger the ramp, whilst the ramp speed is synchronised by the distributed timing signal. The ramp will last approximately 30 minutes and the energy of each circulating beam will eventually reach the 7 TeV nominal value.

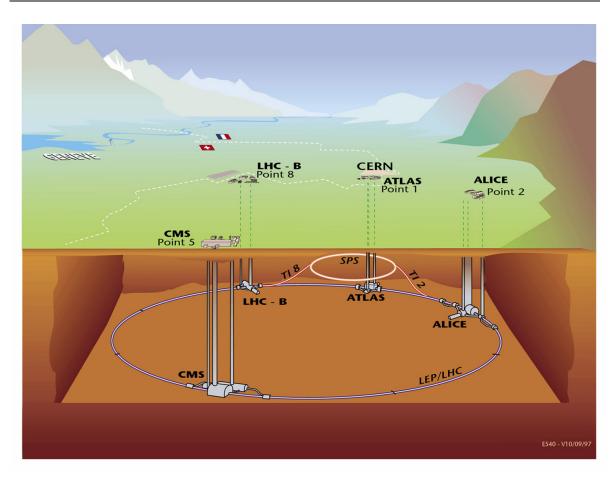

Figure 1-2: LHC Layout. [1]

#### 1.2.3 COLLISION

The high number of bunches circulating in the LHC will be brought together 40 million times per second at four collision points spaced around the ring. These bunch crossings will result in collisions with an event rate of several hundreds of MHz. That is, conditions needed to make new (and maybe unexpected) elementary particles. For these points, detectors are being built to take 'snapshots' of the produced particles and measure their momentum and energy.

Four particle detectors are currently being constructed and will eventually be housed in underground caverns. Figure 1-2 shows their placement in the LHC. They will record the tracks left by debris from the collisions. The primary task of the LHC is to make an initial exploration of the TeV range. The two major LHC detectors, called ATLAS (A Toroidal LHC Apparatus) [3] and CMS (The Compact Muon Solenoid) [4], should be able to accomplish this for any Higgs mass in the expected range. Apart from those, there will be

ALICE (A Large Ion Collider Experiment) [5], which will be built to exploit the unique physics potential of nucleus-nucleus interactions at LHC energies, and LHCb [6], which will carry out precision measurements of CP-violation and rare decays of B mesons. They are scheduled to record their first data from collisions in July 2007.

#### 1.3 LHC CHALLENGES IN ACCELERATOR PHYSICS

In the LHC, the energy available in the collisions between the constituents of the protons (the quarks and gluons) will reach the TeV range, that is about 10 times that of LEP and the Fermilab Tevatron.

#### 1.3.1 THE BEAM-BEAM EFFECT AND BEAM LOSS

When two bunches cross in the centre of a physics detector only a tiny fraction of the particles collide head-on to produce the wanted events. All the others are deflected by the strong electromagnetic field of the opposing bunch. These deflections, which are stronger for denser bunches, accumulate turn after turn and may eventually lead to particle loss. In order to reach the desired luminosity the LHC has to operate as close as possible to this limit. Its injectors, the old PS and SPS, are being refurbished to provide exactly the required beam density.

#### 1.3.2 PARTICLES HAVE TO REMAIN STABLE FOR LONG TIMES

The beams will be stored at high energy for about 10 hours. During this time, the particles make four hundred million revolutions around the machine. Meanwhile the amplitude of their natural oscillations around the central orbit should not increase significantly, because this would dilute the beams, degrade luminosity and causes particle impacting on equipment. This is difficult to achieve, since, in addition to the beam-beam interaction already mentioned, tiny spurious non-linear components of the guiding and focusing magnetic fields of the machine can render the motion slightly chaotic, so that after a large number of turns the particles may be lost.

In the LHC the destabilizing effects of magnetic imperfections is more pronounced at injection energy, because the imperfections are larger owing to persistent current effects in

the superconducting cables, and also because the beams occupy a larger fraction of the coil surrounded cross section. The Dynamic Aperture, within which particles remain stable for the required time, needs to exceed the dimension of the injected beam with a sufficient safety margin. For the time being, no theory can predict with sufficient accuracy the long-term behaviour of particles in non-linear fields. Instead fast computers are being used to track hundreds of particles step by step through the thousands of LHC magnets for up to a million turns. Their results are used to define tolerances for the quality of the magnets at the design stage and during production to limit the particle loss.

#### 1.3.3 BEAM LOSSES AND QUENCH OF MAGNETS

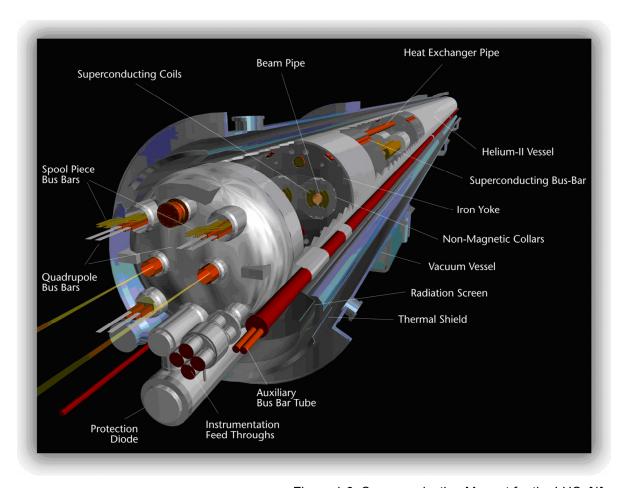

The two magnetic channels will be housed in the same yoke and cryostat, a unique configuration that not only saves space but also gives a 25 % cost saving over separate rings. Figure 1-3 shows this architecture. High energy LHC beams need high magnetic bending fields, because the machine radius was not a parameter which could have been increased to provide gentle curves. To bend 7 TeV protons around the ring, the LHC dipoles must be able to produce fields of 8.36 Tesla, over five times those used a few years ago at the SPS proton-antiproton collider, and almost 100,000 times the earth's magnetic field. Superconductivity makes this possible. This is the ability of certain materials, usually at very low temperatures, to conduct electric current without resistance and power losses. Therefore, higher currents are possible to be applied that will create the necessary high magnetic fields. For comparable power consumption, the LHC can deliver 25 times the energy and 10,000 times the luminosity of the SPS collider.

Figure 1-3: Superconducting Magnet for the LHC. [1]

Despite all precautions the beam lifetime will not be infinite, in other words a fraction of the particles will diffuse towards the beam pipe wall and be lost. In this event, the particle energy is converted into heat in the surrounding material and this can induce a quench of the superconducting magnets or damage the coil, thus interrupting operation from few hours to several months. To avoid this, a collimation system will catch the unstable particles before they can reach the beam pipe wall, so as to confine losses in well shielded regions far from any superconducting element. The LHC combines for the first time a large beam current at very high energy with the most sophisticated superconducting technology. As a consequence, it needs much more efficient collimation and beam loss measurement systems than previous machines.

#### 1.4 LHC Machine Protection

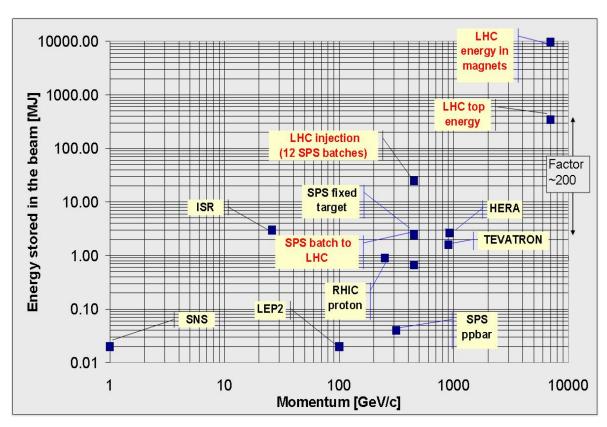

For the LHC both the particle momentum and the beam intensity increases to unprecedented values. The proton momentum is at least a factor of seven above accelerators such as SPS, Tevatron and HERA, whereas the energy stored in the beams is more than a factor of 100 higher. The transverse energy density as relevant factor for equipment damage is a factor of 1000 higher than for other accelerators. Figure 1-4 illustrates the difference in the energy stored in the beam for LHC and other accelerators, as well as the energy stored in the LHC magnets.

Figure 1-4: Comparison of Energy stored in the beam for LHC and other accelerators. [10]

The LHC, with about 8000 magnets powered in 1700 electrical circuits, can suffer several different kinds of accidents or malfunctions that could lead to beam losses if any of those systems fails. Other accidents can be due to aperture restrictions provoked by beam screens, interconnections, vacuum valves or collimator jaws, more than 100, which can obstruct the beam passage.

Those beam losses can happen either in a single turn, with a sudden beam loss, or in progressive losses during numerous turns. One-turn failures are called ultra-fast losses. Multi-turn failures can be divided between very-fast losses, those which happen in less than 10 ms, fast losses, which happen in more than 10 ms and steady losses, where the beam is lost in one second or more. [9]

The machine protection comprises several systems and sub-systems, such as the beam loss related protection, the quench protection, the beam interlock system, and the beam dump system. Here, the introduction will be restricted to those directly linked to the Beam Loss Monitoring system. More information can be found for the rest of the systems here [7].

#### 1.4.1 BEAM LOSS MONITORING SYSTEM (BLM)

In general, the Beam Loss Monitoring (BLM) system converts the signal given by the recording of shower particles into electrical signals and decides if threshold limits are being exceeded. The Beam Permit signal is de-asserted if one detector exceeds the limit and consecutively is transferred to the Beam Dump system by the Beam Interlock system.

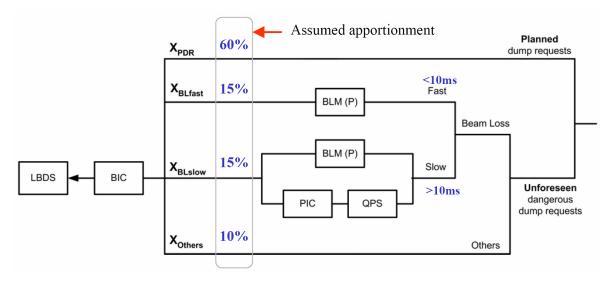

The beam loss measurement system is part of the equipment protection system [13]. The protection as foreseen in the LHC is schematically shown in Figure 1-5. The number of beam dump requests, which reaches the dump system over the machine interlock, is up to 60 % by operator initiated request (inspired distribution by HERA [14]). The remaining dump requests are up to 30 % caused by beam loss initiated dumps and up to 10 % by various other reasons.

Figure 1-5: Dump request distribution and the employment of the beam loss system. [15]

The beam initiated dump requests are equally subdivided in losses with a duration below 10 ms and above. The long losses can be detected in addition with the quench protection system (QPS, PIC). In this case, two independent systems are available for the detection. The short losses can only be detected by the BLM system, augmenting, in this way, its criticality in the machine protection.

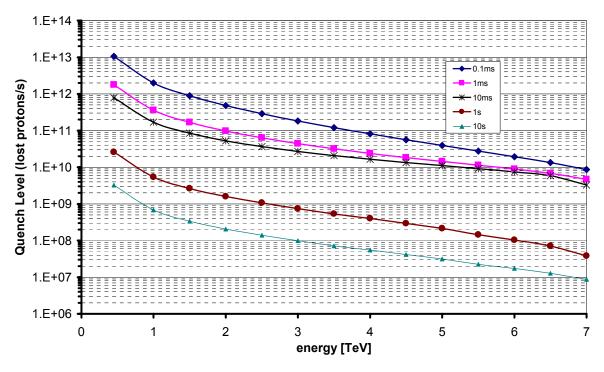

The proton loss initiated quench of magnets is depending on the loss duration and on the beam energy. Figure 1-6 shows a plot of the LHC bending magnets quench level curves as a function of the beam energy for different loss durations. It can be observed that, in the quench level for the same loss duration, there is about three orders of magnitude difference between the injection and the nominal energy. The BLM will need to read the beam energy delivered by the Beam Energy Tracking System (BETS), shown in the following section, to adjust the threshold levels accordingly in order to detect a possible quench.

Figure 1-6: Quench Level curves for various Loss Durations as function of the Beam Energy.

In the case of LHC, a quench of a magnet will create a downtime in the order of hours where in the possibility of its destruction the downtime will be in the order of months to accommodate only its replacement.

#### 1.4.2 BEAM ENERGY TRACKING SYSTEM (BETS)

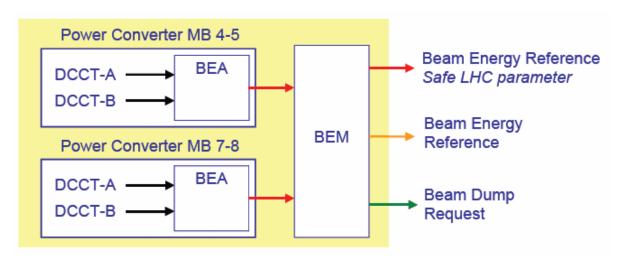

The Beam Energy Tracking System (BETS) binds the bending magnet current to the beam energy. The bending current is measured in two of the eight sectors of the LHC. At each sector the current is measured twice with two independent current transformers (DCCTs). It is then able to distribute the acquired beam energy to the external clients through the Safe LHC Parameters (SLP) system. Figure 1-7 illustrates an overview of the beam energy acquisition by the BETS.

Figure 1-7: Overview of the Beam Energy Acquisition. [12]

The Beam Energy Acquisition (BEA) module acquires and digitises two independent unipolar channels with 16-bit resolution ADCs. The Beam Energy Meter (BEM) module receives four digital measurements proportional to beam energy from the BEA. These measurements are compared within the BEM with a 3 out of 4 logic and a relative error of  $\pm$  0.5%. Failure results in a beam dump request. The mean value of the four measurements is then converted into an absolute beam energy reference through a calibration look-up table.

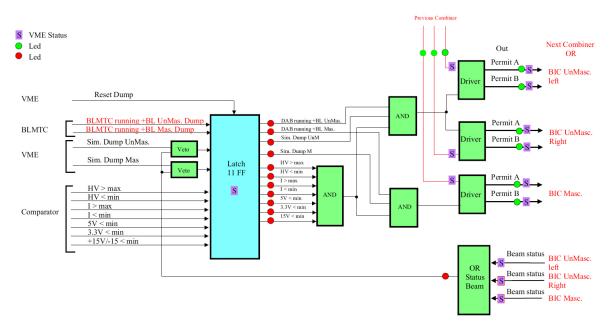

#### 1.4.3 BEAM INTERLOCK SYSTEM (BIS)

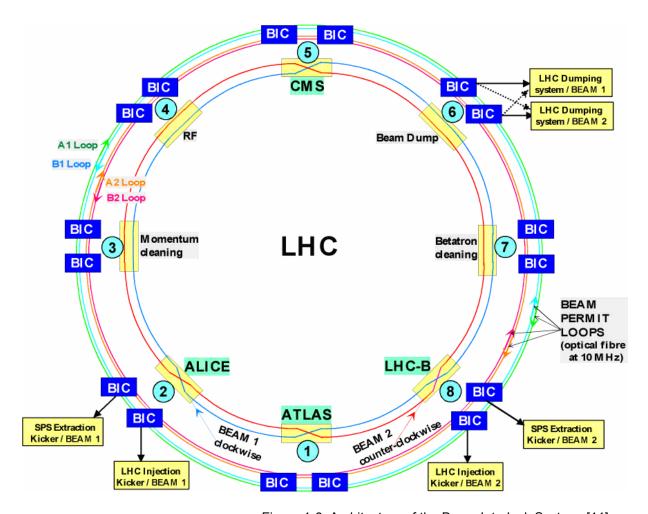

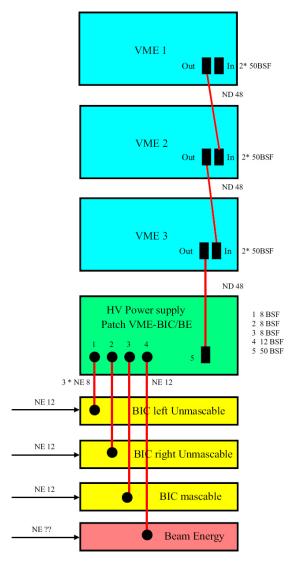

The Beam Interlock System for the LHC is comprised by 16 Beam Interlock Controller (BIC) modules installed right and left from each interaction point (IP). Figure 1-8 illustrates an overview of its architecture.

Figure 1-8: Architecture of the Beam Interlock System. [11]

The controllers are connected by two loops, named Beam Permit Loops. When the loops are broken, the beams are extracted into the beam dump blocks by the Beam Dump System (LBDS). The two loops distinguish between beams I and II.

The system allows breaking one of the loops leading to a dump of only one beam and the LHC has a Beam Dump System for each beam. This property could be used for example during injection where one beam may have been successfully injected but the attempt to inject the other beam leads to a stored beam with unacceptable beam parameters. Another

example is a degraded vacuum in one beam tube, where operation with the other beam will still be possible.

In order to inject beam, the Beam Dump System must be ready, all vacuum valves in the beam tube must be in the "open" position, magnets in the transfer line need to be powered, etc. The Beam Interlock Controllers ensure that these conditions are met.

#### **REFERENCES**

- [1] What is CERN?,

- [online: http://public.web.cern.ch/public/Content/Chapters/AboutCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhatIsCERN/WhitIsCERN/WhitIsCERN/WhitIsCE

- [2] CERN Accelerator Complex webpage,

- [online:http://public.web.cern.ch/public/Content/Chapters/AboutCERN/HowStudyPrtcles/ CERNAccelComplex/CERNAccelComplex-en.html]

- [3] ATLAS public information pages, [online: <a href="http://atlas.ch/">http://atlas.ch/</a>]

- [4] CMS Outreach, [online: <a href="http://cmsinfo.cern.ch/Welcome.html">http://cmsinfo.cern.ch/Welcome.html</a>]

- [5] ALICE public information pages, [online: <a href="http://na49info.cern.ch/alice/html/intro">http://na49info.cern.ch/alice/html/intro</a>]

- [6] LHCb public information pages,

- [online: http://lhcb-public.web.cern.ch/lhcb-public/default.htm]

- [7] F.Bordry, R.Denz, K-H.Mess, B.Puccio, F.Rodriguez-Mateos and R.Schmidt, "*The Architecture of the Machine Protection System of the LHC*", LHC Project Report 521.

- [8] F.Bordry, R.Denz, K-H.Mess1, B.Puccio, F.Rodriguez-Mateos and R.Schmidt, "Machine Protection for the LHC: Architecture of the Beam and Powering Interlock Systems", CERN, LHC Project Report 521, Geneva, 21 December 2001.

- [9] R.Schmidt et al., "Beam loss scenarios and strategies for machine protection at the LHC", HALO '03, Montauk, NY, 19-23 May 2003

- [10] R.Schmidt, "Machine Protection System(s) Overview", LHC Project Workshop Chamonix XIV.

- [11] Engineering Specification, "The Beam Interlock System For The LHC", LHC Project Document No. LHC-CIB-ES-0001-00-10, version 1.0, 17-02-2005.

- [12] E.Carlier, G.Gräwer, N.Voumard, R.Gjelsvik, "Update on the Beam Energy Tracking System", presentation given at the LHC Machine Protection Working Group, 03/06/2005.

- [13] B. Dehning, "Beam loss monitor system for machine protection", 7th European Workshop on Beam Diagnostics and Instrumentation for Particle Accelerators, DIPAC'05, Lyon, France, 06 08 Jun 2005.

[14] K. Wittenburg, "Quench levels and transient beam losses at HERAp", Workshop on Beam generated heat deposition and quench levels for LHC magnets, CERN, March 2005.

[15] R. Filippini, B. Dehning, G. Guaglio, F. Rodriguez-Mateos, R. Schmidt, B. Todd, J. Uythoven, A. Vergara-Fernandez, M. Zerlauth, "*Reliability Assessment of the LHC Machine Protection System*", Particle Accelerator Conference PAC 2005, Knoxville, TN, USA, 16 - 20 May 2005.

# 02

**Beam Loss Monitoring System for the LHC**

## **Chapter 2. Beam Loss Monitoring System for the LHC**

Beam Loss Monitors are devices used to measure and localise beam losses over an accelerator. A Beam Loss Monitoring (BLM) system should be able to determine the number of lost particles or, in a more dramatic sense, to request a beam dump in those cases which are considered seriously dangerous for the machine.

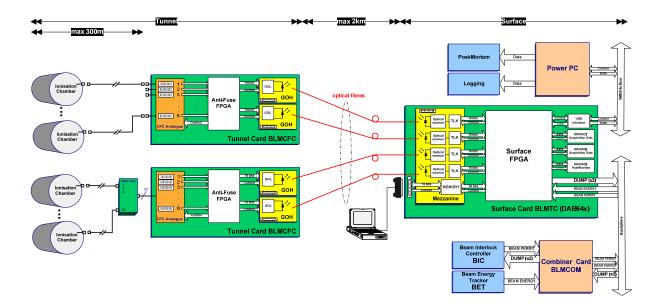

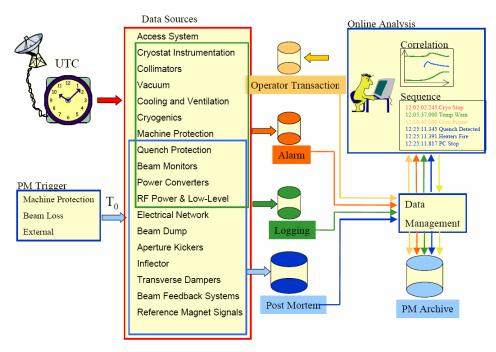

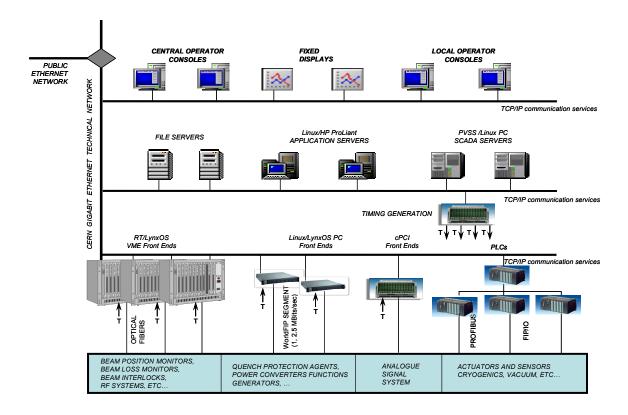

The complete BLM system for the LHC can be easily divided geographically by the installations at the tunnel and at the surface building. The basic structures of the two parts communicating over an optical link are shown in Figure 2-1.

Figure 2-1: LHC Beam Loss Monitoring System Overview.

Around 3600 Ionization Chambers are the detectors of the system. A set of up to eight of them can be connected to each of the tunnel cards. In those tunnel cards, named BLMCFCs, the digitisation of the detector signal is done by using Current-to-Frequency converters (CFC) and Analogue-to-Digital converters (ADC). A Field Programmable Gate Array (FPGA) device acquires the digitised data and transmits them to the surface using Gigabit Optical Links. At the surface installations, the data are received by the data analysis modules, named BLMTCs.

The backbone of those cards, which is also an FPGA device, will analyse by keeping histories of those data and decide whether a beam dump request should be initiated by comparing those histories with predefined threshold values. Each surface card receives data from two tunnel cards, meaning that it can treat up to sixteen channels. Finally, the BLMTC cards are accommodated in VME crates that include Combiner cards for concentrating the beam dump requests and distributing the beam energy.

#### 2.1 BEAM LOSS DETECTORS

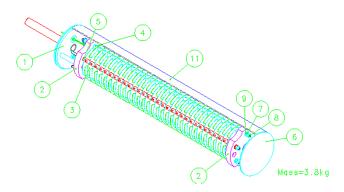

The majority of the detectors of the BLM system will be ionisation chambers. For regions with very high loss rates, secondary emission monitors (SEM) are foreseen as well. The ionisation chamber consists of a stack of parallel electrodes, which is inserted in a stainless steel tube. The schematic drawing of the ionisation chamber used for the LHC can be seen in Figure 2-2. The volume of the chamber is filled with gas under normal pressure. The electrical field strength in between of the electrodes is 3 kV/cm. The only passive electronic components are a resistor and a capacitor of a low pass filter mounted at the feedthroughs of the chambers. This filter smoothes drift voltage variations and, in the case of a break down of the voltage power supply, it keeps the drift voltage almost constant at the electrodes of the chamber. The correct functioning of the ionisation chamber is therefore ensured for minutes after switch off, even in case of a break down.

Figure 2-2: Drawing of the LHC ionisation chamber. [16]

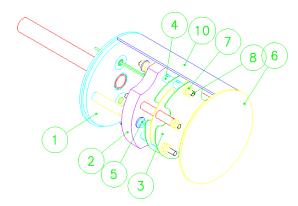

The SEM detector will be based on the same design as the ionisation chamber. Instead of having the electrode volume filled with a gas it will be under vacuum and only one sensitive foil will be used to reduce the resolution. The schematic drawing of the SEM detector used for the LHC can be seen in Figure 2-3.

Figure 2-3: Drawing of the secondary emission monitor. [16]

It is foreseen to have one tube shape assembly with a short SEM part on one side and a longer ionisation chamber part on the other side. Both detectors will be mounted on the outside of the cryostat in the horizontal plane given by the two vacuum pipes of the LHC magnets. At this position, the secondary particle flux is highest and the best separation of the losses from the two beams is reached.

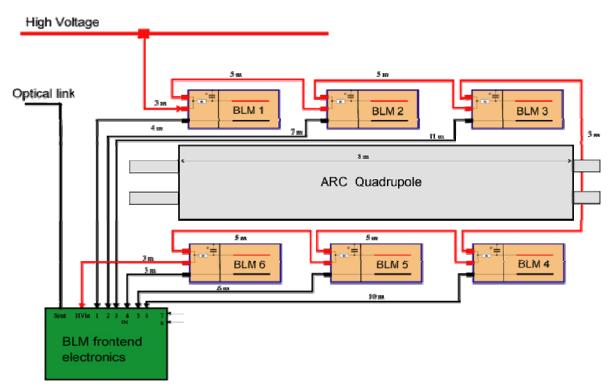

From shower simulations at the different loss locations [17], it was found that a set of six detectors around the quadrupoles is sufficient for localising the beam losses and to distinct them between the two beams. Figure 2-4 illustrates the arrangement of the detectors around the quadrupole magnet, as well as their interconnection.

Figure 2-4: Arrangement of the Detectors around the Magnet. [18]

#### 2.2 FRONT-END ELECTRONICS

The placement of the BLM front-end electronics for the Left and Right regions in the arc of each Interaction Point (IP) is in a crate below the quadrupole magnet, where also other systems' electronics are mounted. For the Middle regions of the straight sections, where increased levels of radiation are occurring, the signals are transported to the closest stub tunnel (alcove) before digitisation.

#### 2.2.1 THE BLMCFC CARD

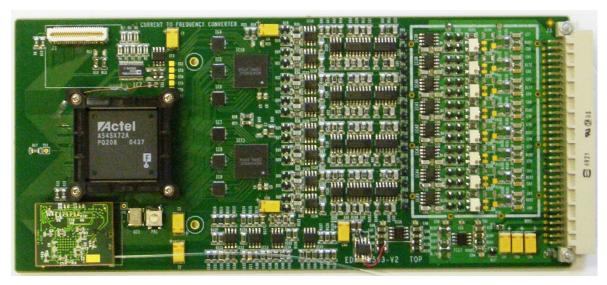

The FPGA used in the front-end electronics is from Actel. The 54SX72A device, belonging in the SX-A [19] family of Actel's devices, comes in a 208 pin PQFP (plastic quad flat pack) package and provides 72,000 system gates for building its functionality. It belongs to the one-time-programmable (OTP) type of devices using electrically fusible links, a feature Actel calls AntiFuse technology. While re-programmability is generally desirable, OTP technologies like that used in Actel's antifuse families provide other important performance, security, and radiation-tolerant features that are necessary for many critical designs like the BLM system.

The Current-to-Frequency Converter was built using off-the-shelves components. The basic elements comprising its functionality are an amplifier, the OPA627, a JFET, the J176, a Comparator, the NE521, and a monostable, the 74HCT123. More about the functionality achieved will be shown in the following section.

The AD74240 [20] is a Quad 12-bit ADC, thus, two of those CMOS devices will be necessary in the card to cover the eight connected detectors. It operates with a sampling speed of 40Ms/s and provides the data in a parallel output. The outputs from the ADC are in Low Voltage Differential Signaling (LVDS) levels using the Double Data Rate (DDR) scheme.

The signalling scheme used for the digital data output of the ADC uses the LVDS standard but the FPGA is built with CMOS level I/Os. This requires a level converter next to each ADC. An LVDS to CMOS transceiver ASIC is used to this purpose. The LVDS\_MUX

[21] CMOS device can receive and convert eight LVDS signals, thus six of them will be used for each card.

Figure 2-5: Picture of the Tunnel (BLMCFC) Card.

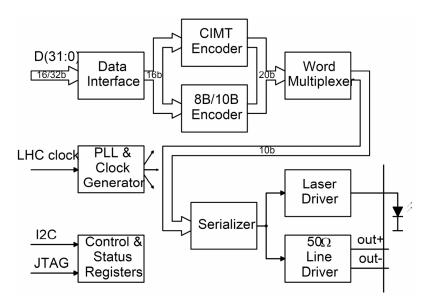

Two of the GOL (Gigabit Optical Link), also belonging to the CERN custom-made ASICs with radiation tolerant design, will be used for each card. They include the analogue parts needed to drive the laser, an algorithm running that corrects SEU and the output is providing the data already with 8b/10b encoding for either 16 or 32-bit input. It also provides error reporting, like number of SEU detected or loss of synchronisation, that will be used to discover failing components.

In Figure 2-5, it is shown a picture of the frond-end card, named BLMCFC, which accommodates all the above-mentioned components. More about the communication protocols used will be discussed in the following chapter.

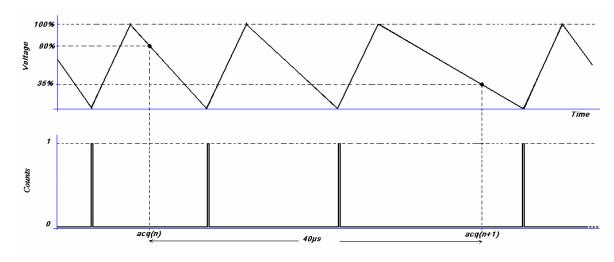

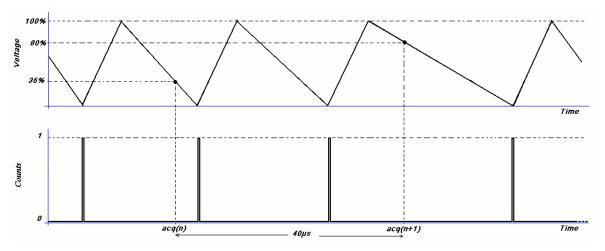

#### 2.2.2 CURRENT-TO-FREQUENCY CONVERTER (CFC)

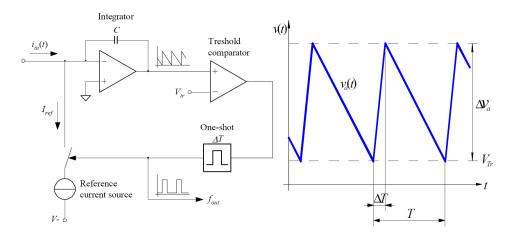

The particle losses are measured, in the analogue part in the front-end card, and transmitted to the surface, where the final evaluation takes place. To measure the detector signal, a current-to-frequency converter (CFC) was designed. It works on the principle of balanced charge and is shown in Figure 2-6.

Figure 2-6: Principle of the balanced charge Current-to-Frequency Converter. [17]

The signal, i.e. the current induced from the detector, is integrated during the whole period T. If a constant chamber current is assumed, the integrator output ramps down with a constant slope. After reaching a threshold, the reference current *Iref* is induced into the summing node of the op-amp for a fixed time  $\Delta T$ , driving the integrator output back again.

The output frequency is related to the chamber current by

$$f = \frac{\bar{i}_{in}}{I_{ref}\Delta T}$$

[2-1]

#### 2.2.2.1 CFC CHARACTERISTICS

The characteristics of the CFC circuit designed and the ionisation chamber at use can be seen in Table 2-1. The use of the CFC was dictated mainly by the high dynamic range needed for the BLM system. The CFC has the ability to give a value of 5.00E+08, much higher than all other options evaluated in a previous study [22].

Table 2-1: Current-to-Frequency Converter and Ionisation Chamber Specifications.

|            | CFC                   | Ionisation Chamber |                     |  |  |

|------------|-----------------------|--------------------|---------------------|--|--|

| Frequency  | 0.01 - 5.00E+06 Hz    | Length             | 19cm                |  |  |

| Current    | 2.5 - 1.00E+06 pA     | Surface            | 63cm <sup>2</sup>   |  |  |

| Dynamic    | 5.00E+08              | Volume             | 1000cm <sup>3</sup> |  |  |

|            | 200 pC/clock          | Resolution         | 2500ch./Mip         |  |  |

| Resolution | 1.25E+09 elect./clock | High Voltage       | 1500V               |  |  |

|            | 5.00E+05 Mips/clock   | Rise Time          | ~100ns              |  |  |

| Clock max  | 5.00E+02 clock/0.1ms  | Fall Time          | ~100µs              |  |  |

The secondary particle flux at the location of the detectors, normalised to the number of inducing protons is called fluence. The fluence distribution expected in the LHC is sought to be resolved with simulations of proton impacts at the magnets. The uncertainty of these simulations is mainly determined by uncertainties in the shower developments and in the knowledge of the geometry. The current estimated minimum and maximum fluence levels can be found in Table 2-2.

Table 2-2: Estimated Fluence Levels at 0.45 and 7 TeV.

| Fluence |                           | 0.45     | TeV      | 7TeV     |          |  |

|---------|---------------------------|----------|----------|----------|----------|--|

|         |                           | Min Max  |          | min      | Max      |  |

| BL ARC  | Mips/cm <sup>2</sup> /p   | 5.00E-04 | 3.00E-03 | 8.00E-03 | 4.00E-02 |  |

| BL      | Mips/63cm <sup>2</sup> /p | 3.15E-02 | 1.89E-01 | 5.04E-01 | 2.52E+00 |  |

Applying the estimated fluence levels to the characteristics of the CFC and the Ionisation Chamber it is possible to calculate the number of counts expected to be collected for different time periods. Table 2-3 and Table 2-4 show a summary for the minimum and maximum number of counts expected, as well as, the number of counts needed to reach the magnet quench level for beam energies of 450GeV and 7TeV respectively.

Table 2-3: Number of Counts Produced at 0.45TeV.

| 0.45TeV   |          |          |          |            |             |             |             |              |

|-----------|----------|----------|----------|------------|-------------|-------------|-------------|--------------|

|           |          | Fluer    | псе      |            |             |             |             |              |

|           | p/m/s    | Min      | Max      | Resolution | Int.time(s) | Resolution  | No co       | ounts        |

|           |          | (Mips/63 | cm2/p)   | (ch/mip)   |             | elct./count |             |              |

| min. rate |          |          |          |            |             |             |             |              |

|           | 5.00E+08 | 3.15E-02 | 1.89E-01 | 2.50E+03   | 1.00E-04    | 1.25E+09    | 0.00315     | 0.01890      |

|           | 3.00E+08 | 3.15E-02 | 1.89E-01 | 2.50E+03   | 2.50E-03    | 1.25E+09    | 0.04725     | 0.28350      |

|           | 4.00E+05 | 3.15E-02 | 1.89E-01 | 2.50E+03   | 1.00E+01    | 1.25E+09    | 0.25200     | 1.51200      |

|           | 1.00E+05 | 3.15E-02 | 1.89E-01 | 2.50E+03   | 1.00E+02    | 1.25E+09    | 0.63000     | 3.78000      |

| max. rate |          |          |          |            |             |             |             |              |

|           | 2.00E+13 | 3.15E-02 | 1.89E-01 | 2.50E+03   | 1.00E-04    | 1.25E+09    | 126         | 756          |

|           | 2.00E+12 | 3.15E-02 | 1.89E-01 | 2.50E+03   | 2.50E-03    | 1.25E+09    | 315         | 1,890        |

|           | 1.00E+09 | 3.15E-02 | 1.89E-01 | 2.50E+03   | 1.00E+01    | 1.25E+09    | 630         | 3,780        |

| Quench    |          |          |          |            |             |             |             |              |

|           | 2.58E+13 | 3.15E-02 | 1.89E-01 | 2.50E+03   | 4.00E-05    | 1.25E+09    | 64.99295    | 389.95767    |

|           | 1.08E+13 | 3.15E-02 | 1.89E-01 | 2.50E+03   | 1.00E-04    | 1.25E+09    | 67.98236    | 407.89419    |

|           | 1.19E+12 | 3.15E-02 | 1.89E-01 | 2.50E+03   | 2.50E-03    | 1.25E+09    | 187.55911   | 1,125.35468  |

|           | 3.20E+09 | 3.15E-02 | 1.89E-01 | 2.50E+03   | 1.00E+01    | 1.25E+09    | 2,016.00000 | 12,096.00000 |

|           | 9.50E+08 | 3.15E-02 | 1.89E-01 | 2.50E+03   | 1.00E+02    | 1.25E+09    | 5,985.00000 | 35,910.00000 |

|           |          |          |          |            |             |             |             |              |

| 7TeV      |            |          |          |          |             |             |            |              |

|-----------|------------|----------|----------|----------|-------------|-------------|------------|--------------|

|           |            | Flue     | nce      |          |             |             |            |              |

|           | p/m/s      | Min      | Max      |          | Int.time(s) | Resolution  | No co      | ounts        |

|           | l .        | (Mips/63 | cm2/p)   | (ch/mip) |             | elct./count |            |              |

| min. rate | F 00F : 00 | E 04E 04 | 0.505.00 | 0.505.00 | 4.005.04    | 4.055.00    | 0.050400   | 0.05000      |

|           | 5.00E+08   |          | 2.52E+00 |          | 1.00E-04    |             | 0.050400   | 0.252000     |

|           | 3.00E+08   | 5.04E-01 |          |          | 2.50E-03    |             | 0.756000   | 3.780000     |

|           | 4.00E+05   | 5.04E-01 | 2.52E+00 | 2.50E+03 | 1.00E+01    | 1.25E+09    | 4.032000   | 20.160000    |

|           | 1.00E+05   | 5.04E-01 | 2.52E+00 | 2.50E+03 | 1.00E+02    | 1.25E+09    | 10.080000  | 50.400000    |

| max. rate | <u>,</u>   |          |          |          |             | _           |            |              |

|           | 2.00E+13   | 5.04E-01 | 2.52E+00 | 2.50E+03 | 1.00E-04    | 1.25E+09    | 2,016      | 10,080       |

|           | 2.00E+12   | 5.04E-01 | 2.52E+00 | 2.50E+03 | 2.50E-03    | 1.25E+09    | 5,040      | 25,200       |

|           | 1.00E+09   | 5.04E-01 | 2.52E+00 | 2.50E+03 | 1.00E+01    | 1.25E+09    | 10,080     | 50,400       |

| Quench    |            |          |          |          |             |             |            |              |

|           | 2.18E+10   | 5.04E-01 | 2.52E+00 | 2.50E+03 | 4.00E-05    | 1.25E+09    | 0.878753   | 4.393764     |

|           | 1.22E+10   | 5.04E-01 | 2.52E+00 | 2.50E+03 | 1.00E-04    | 1.25E+09    | 1.229202   | 6.146011     |

|           | 6.05E+09   | 5.04E-01 | 2.52E+00 | 2.50E+03 | 2.50E-03    | 1.25E+09    | 15.247176  | 76.235880    |

|           | 1.24E+07   | 5.04E-01 | 2.52E+00 | 2.50E+03 | 1.00E+01    | 1.25E+09    | 124.992000 | 624.960000   |

|           | 8.26E+06   | 5.04E-01 | 2.52E+00 | 2.50E+03 | 1.00E+02    | 1.25E+09    | 832.608000 | 4,163.040000 |

|           |            |          |          |          |             | :           |            | ,            |

Table 2-4: Number of Counts Produced at 7TeV.

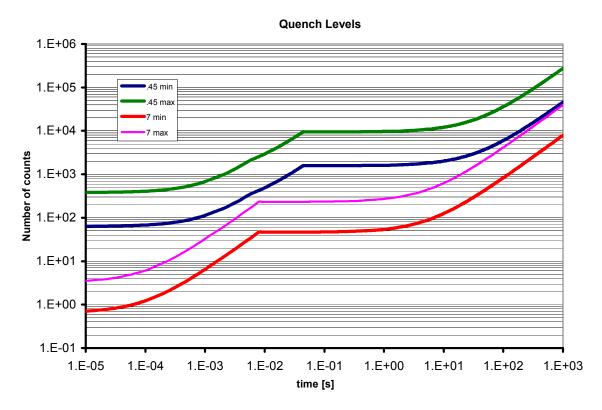

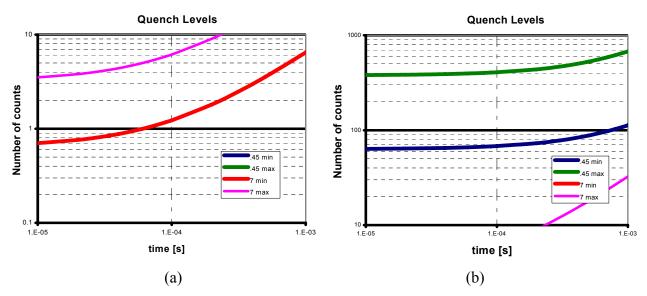

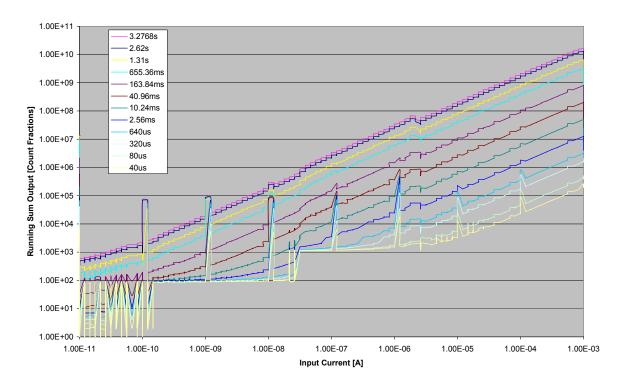

Figure 2-7 shows a plot (using a logarithmic scale) of the number of counts, which will be needed to reach the quench level of a magnet for different integration times. It was calculated using the fluence levels estimated from simulations shown previously.

Figure 2-7: Quench Levels defined by number of counts.

Figure 2-8: Quench Levels defined by number of counts (zoom in 100µs region).

The number of CFC output counts needed, when the accelerator has 7TeV of energy, to exceed the quench level is just around one (see Figure 2-8a), where in the similar case but for lower energies (see Figure 2-8b) it is significantly larger.

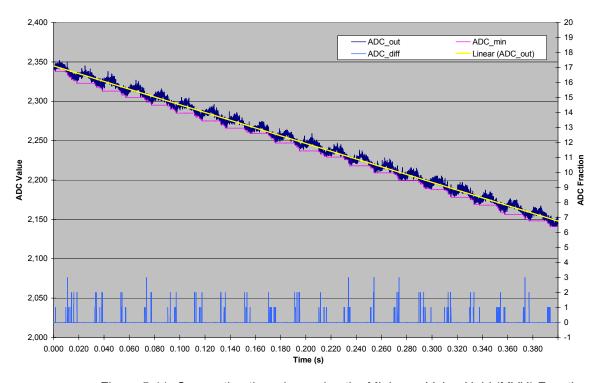

Reaching in some cases the quench level with a value that is equal to the resolution of the CFC output is a limitation that is only possible to be overcome by increasing the dynamic range of the system. For that reason an ADC was in addition decided to be used. The intention is to cover the region below the one count with the ADC and provide a more accurate reading when very slow losses are occurring. The idea lies in measuring the output of the integrator and thus knowing the discharge state of its capacitor at the time of the acquisition. Using, in later stages, some simple pre-processing of those data it will be possible to be merged with the data from the CFC counter.

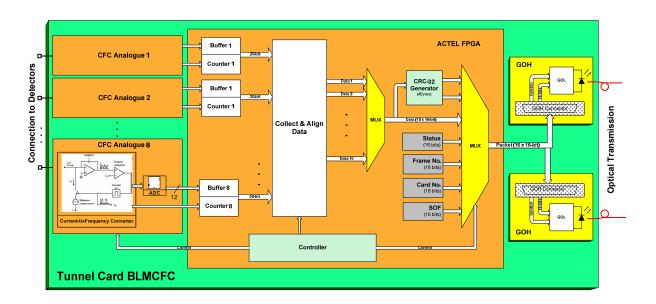

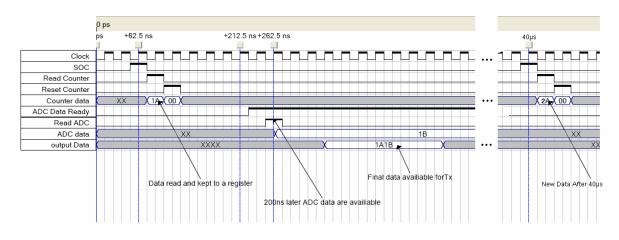

## 2.2.3 FRONT-END FPGA PROCESSES

The functionality that the BLMCFC card will need to exhibit can be simply described as the acquisition of the data produced, by the counter and the ADC, and the production of the packet to be transmitted. A block diagram of the BLMCFC card functionality is illustrated in Figure 2-9.

In more detail, the main tasks assigned to be performed by its FPGA would be, to measure the frequency output of eight CFCs and read the digitized voltage of the feedback capacitor by the ADCs.

In addition, it will collect the status information for the high tension, for the system's temperature and for any possible CFC errors. It will count the number of packets transmitted and hold a unique number, to be used as the Card ID. Finally, all the above data collected will be multiplexed and word aligned for transmission.

In parallel to the data being forwarded to the optical link, a CRC encoding process will calculate a checksum for this packet and append it to provide error detection capabilities to the system. The collected packet transmission will be done through a gigabit optical link that the card will control. More about the data transmitted and the link utilised will be discussed in Chapter 3.

Figure 2-9: Block Diagram of the BLMCFC.

## 2.3 OPTICAL FIBRES

Optical fibres will be used to support the backbone of the data communication networks in the LHC. The optical fibres are installed in mini-tubes, which may contain up to 70 fibres each. The mini-tubes are inserted in protective ducts, which can be directly buried in surface trenches or laid on cable trays, where such infrastructure is available. Fibre "blowing" technology is used wherever possible in order to facilitate fibre maintenance and future extensions. [23]

The cables situated in the LHC tunnel will be subject to radiation, which will damage the fibre over time. It is expected that the light transmission capability of the fibre will deteriorate so much that it must be replaced in the most exposed zones of the machine after every 3-5 years of operation at nominal beam intensity. The installation technique, using mini-tubes contained in ducts, lends itself to rapid replacement of defective fibres. The optical characteristics of the fibres in the main fibre paths will be continuously monitored. Based on trend analysis from the monitoring system, the replacement of defective fibres can be planned within the normal maintenance windows during machine operation. The BLM system will perform a similar monitoring of all its optical components. This procedure will be discussed in Chapter 8.

For the transmission of the BLM data from the tunnel to the surface installation, it is foreseen to multiplex the six signals from the detectors around every quadrupole magnet with two spare channels. This is done mainly to allow the possibility of adding two more "mobile" ionisation chambers, if at a later stage that is found necessary.

This will result in 368 optical fibres, to cover the left and right regions, that include two spare channels per fibre, and 197 optical fibres to cover the middle regions of the LHC. All the data transmissions for the BLM system were decided to have some sort of redundancy as a measure of improving the reliability and the availability of the whole system. In this context, the optical communication channel has been doubled making the total number of optical fibres needed for the BLM system equal to 1130.

# 2.4 SIGNAL RECEPTION AND PROCESSING ELECTRONICS

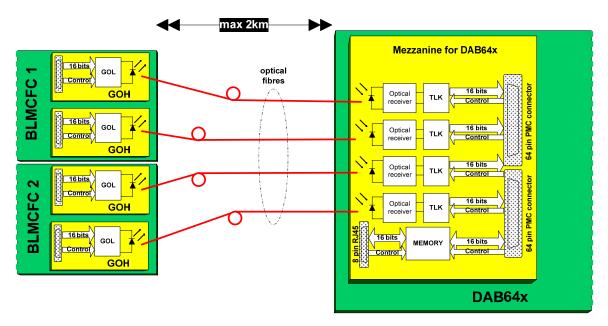

A VME card, that provides the processing power, and a mezzanine card, that links the tunnel with this surface installation, comprise the BLMTC processing module.

Its main task will be to analyse the acquisition data, by keeping a history of those data and calculating various moving sum windows for each detector, and decide whether a dump request should be initiated, by comparing those histories with predefined threshold values. Additionally, it will need to include the back-end of the optical links. Each module will need to host the optical receiver parts for four optical links, meaning that it can treat up to 16 channels.

Those modules will establish communication with the VME-bus but at the same time will be able to work autonomously for protection against main CPU failures. Data will be sent over the VME-bus for on-line viewing and storage by the Logging and Post-Mortem systems.

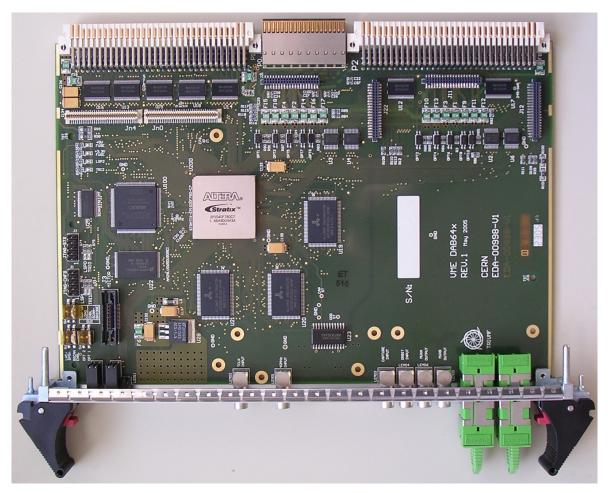

# 2.4.1 THE DAB64x CARD

The data analysis card is based on the general purpose PCB that was implemented for the whole Beam Instrumentation group, named DAB64x [24]. It is comprised from an Altera Stratix [25] FPGA, an Altera MAX CPLD [26] for power-on configuration and VME functionality, and three SRAM memories. The functionality of the system is realised by using different firmware on the FPGA and CPLD devices, and different mezzanine cards that can be placed on either of the six general-purpose connectors available.

The whole Stratix family of FPGAs offers various devices that their features can include from 10,570 to 79,040 Logic Elements, packages that have from 672 to 1,508-Pin FBGAs (FineLine Ball Grid Array) and up to 7,427,520 RAM bits in embedded memory blocks. The DAB64x card was designed with the intention to serve as a processing module for various systems except the BLMS.

For this reason, it was proposed the implementation of the PCB layout to support the possibility of a later exchange of the device within the same family, a feature called vertical migration. Vertical migration [27] means that it is possible to migrate to devices whose dedicated pins, configuration pins, and power pins are the same for a given package across different device densities. Table 2-5 shows the different package options provided by the Stratix family. It was finally decided to allow migration between the EP1S10, EP1S20, EP1S25, EP1S30, and EP1S40 devices in the 780-pin FBGA package.

Table 2-5: Stratix Package Options & I/O Pin Counts. [27]

| Device | 672-Pin<br>BGA | 956-Pin<br>BGA | 484-Pin<br>FBGA | 672-Pin<br>FBGA | 780-Pin<br>FBGA | 1,020-Pin<br>FBGA | 1,508-Pin<br>F BGA |

|--------|----------------|----------------|-----------------|-----------------|-----------------|-------------------|--------------------|

| EP1S10 | 345            |                | 335             | 345             | 426             |                   |                    |

| EP1S20 | 426            |                | 361             | 426             | 586             |                   |                    |

| EP1S25 | 473            |                |                 | 473             | 597             | 706               |                    |

| EP1S30 |                | 683            |                 |                 | 597             | 726               |                    |

| EP1S40 |                | 683            |                 |                 | 615             | 773               | 822                |

| EP1S60 |                | 683            |                 |                 |                 | 773               | 1,022              |

| EP1S80 |                | 683            |                 |                 |                 | 773               | 1,203              |

The FPGA to be used for the BLM system will be the EP1S40, which has 41,250 LE, 615 user I/O pins, and 400KBytes of internal memory as available resources for the system to be built from. At the same time, the Beam Position Monitor (BPM) system, for example, will be able to use the same module but populated with the EP1S20 device. Table 2-6 shows the FPGA features for each of the devices available to be used in the DAB64x card.

Table 2-6: Stratix Device Family Features. [27]

| Feature                     | Device  |           |           |           |           |

|-----------------------------|---------|-----------|-----------|-----------|-----------|

|                             | EP1S10  | EP1S20    | EP1S25    | EP1S30    | EP1S40    |

| Logic Elements              | 10,570  | 18,460    | 25,660    | 32,470    | 41,250    |

| M512 RAM blocks (32×18bits) | 94      | 194       | 224       | 295       | 384       |

| M4K RAM blocks (128×36bits) | 60      | 82        | 138       | 171       | 183       |

| M-RAM blocks (4K ×144 bits) | 1       | 2         | 2         | 4         | 4         |

| Total RAM bits              | 920,448 | 1,669,248 | 1,944,576 | 3,317,184 | 3,423,744 |

| DSP blocks                  | 6       | 10        | 10        | 12        | 14        |

| Embedded multipliers        | 48      | 80        | 80        | 96        | 112       |

| PLLs                        | 6       | 6         | 6         | 10        | 12        |

| Maximum user I/O pins       | 426     | 586       | 597       | 597       | 615       |

Additionally, the BLMTC module includes three of the AS7C33512PFS32A/36A [28] high-performance CMOS 16-Mbit synchronous Static Random Access Memory (SRAM) devices. Each of them is organized as 524,288 words x 32/36 and it incorporates a two-stage register-register pipeline for higher frequency throughput.

Figure 2-10: Picture of the BLMTC Processing Module.

Figure 2-10 shows a picture of the final version of the DAB64x card. The front-panel is mounted with handles to allow easier insertion to the VME64x backplane of the three 5-row connectors, as well as the two double E2000/APC adapters for the optical fibre separations.

## 2.4.2 THE BLM MEZZANINE CARD

The packet will be transmitted through the optical link will arrive first to a mezzanine card. The intention is to include only the photodiode and only necessary electronics on the mezzanine in order to keep it as minimal as possible. The synchronisation and decoding could be assigned to be executed by the FPGA placed on the card but instead a more dedicated chipset (that includes an 8B/10B decoder) is added in the mezzanine for this process.

As a result, the BLM mezzanine card was constructed to include all necessary components for the four gigabit optical receivers and one Mbit of Flash memory for system specific data. The data are delivered to the DAB64x card through two connectors. Those connectors used for the mezzanine are 2 x 64pin PMC connectors that will provide the power supply signals, that is, the 3.3V, 5V and GND, as well as, connection to 114 FPGA I/O pins. A detailed explanation of the choices used and the final implementation of the BLM mezzanine can be found in the following Chapter 3.

The advantage of keeping those design constraints and adding a mezzanine card is that the main card will maintain the universality to be used for more applications except the BLM.

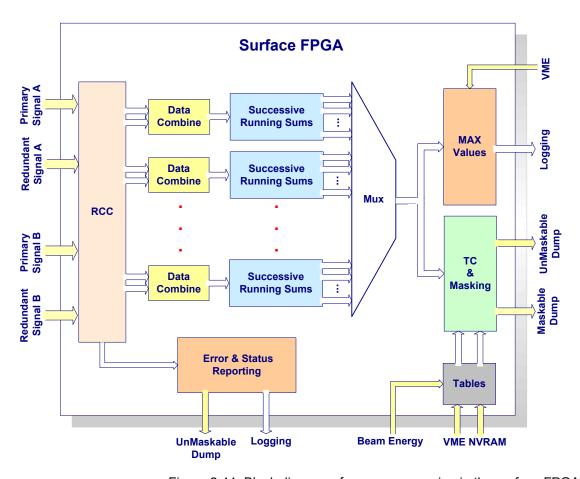

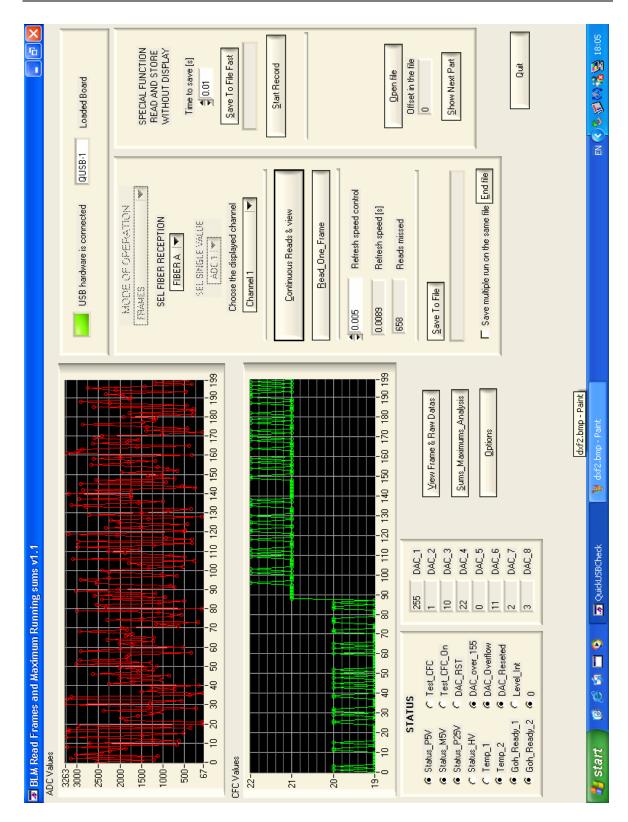

## 2.4.3 SURFACE FPGA PROCESSES

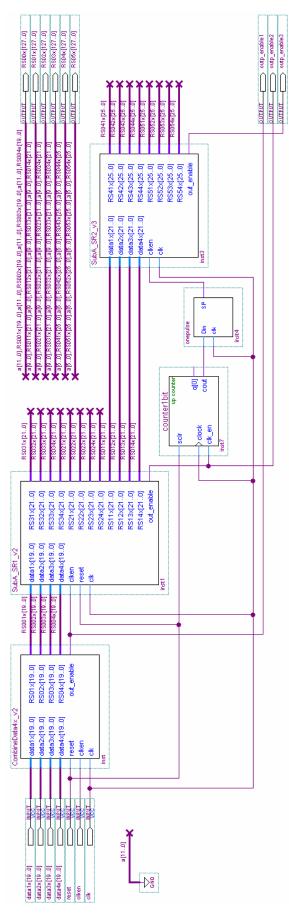

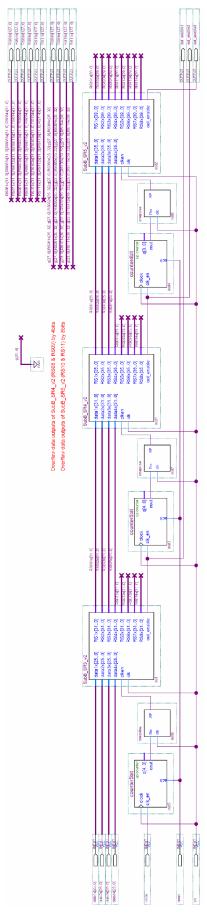

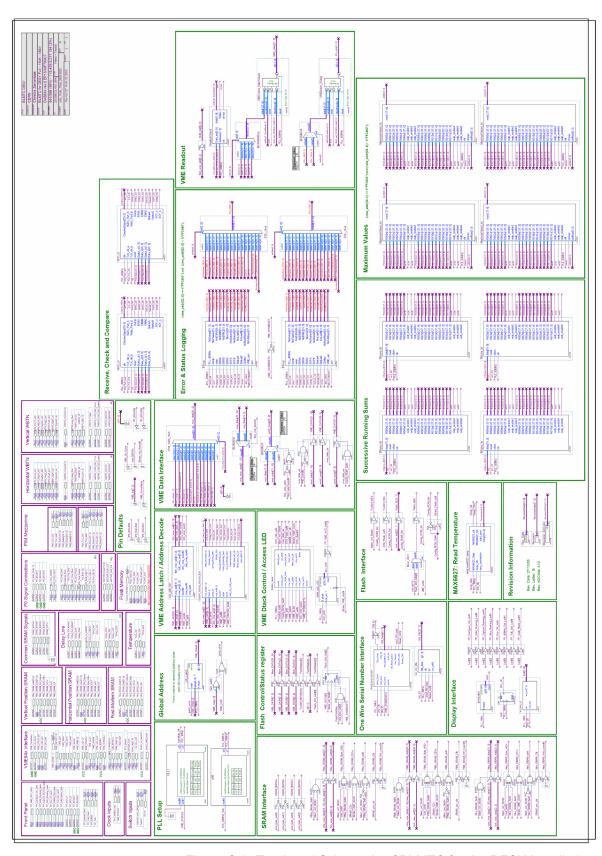

The processes assigned to the surface FPGA will be described in detail on the following chapters. Figure 2-11 illustrates an overview of the main BLMTC processes in the FPGA.

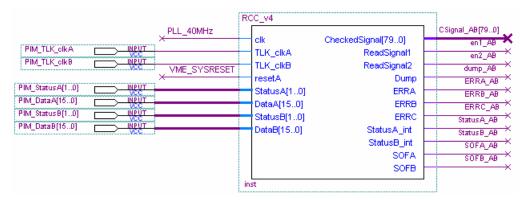

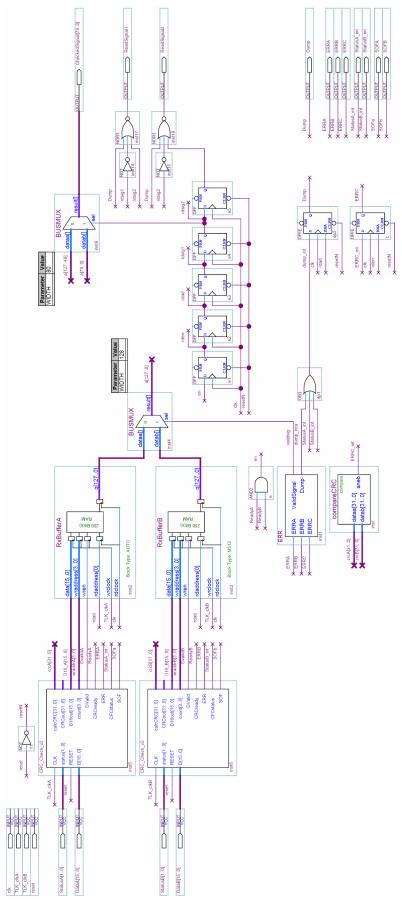

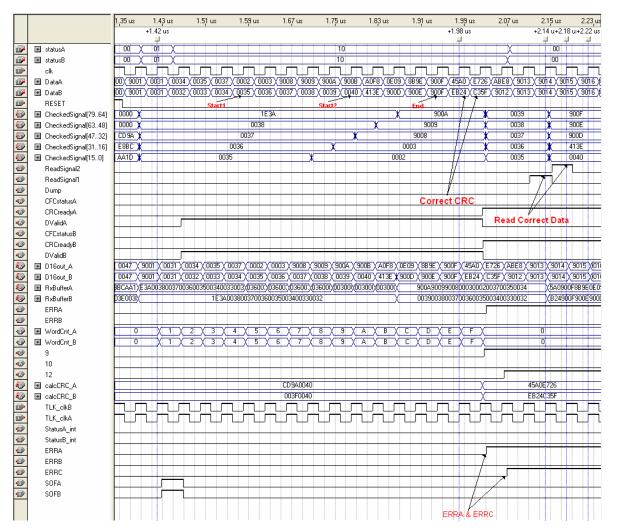

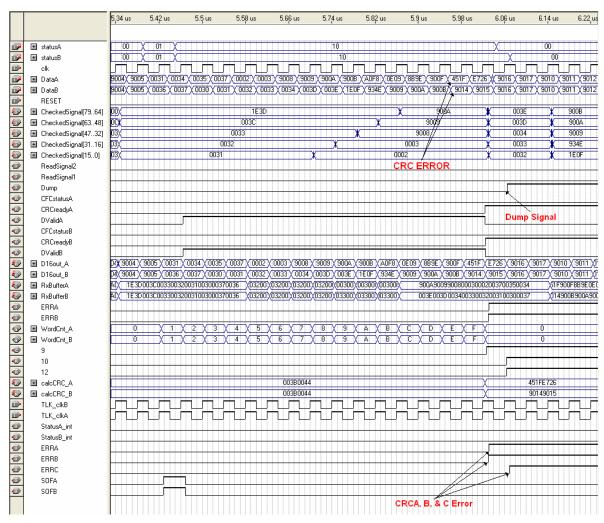

The RCC (Receive, Check and Compare) process (discussed in Chapter 4) will receive, deserialise and decode the transmitted packets. It will check for errors on both transmissions and compare the packets in order to select one error-free packet.

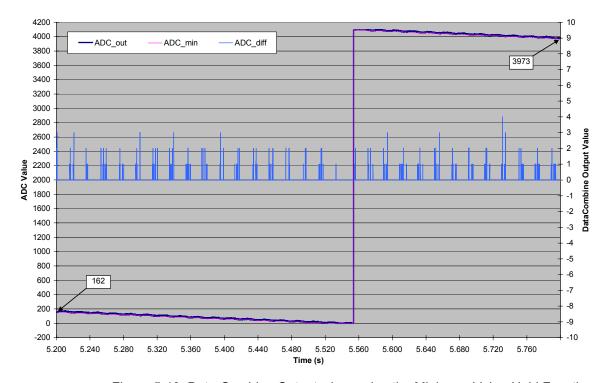

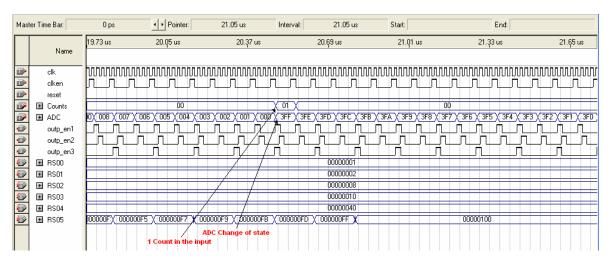

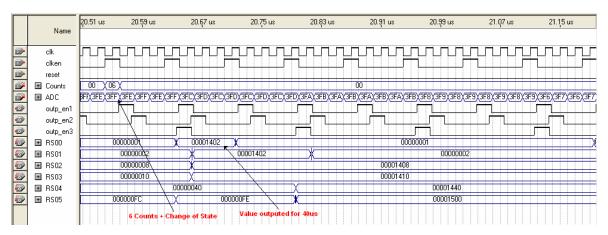

The Data-Combine process (discussed in Chapter 5) will receive the two types of data, the counter and the ADC data, coming from the same detector and will merge them into one value, filtering at the same time noise passing through the ADC circuitry.

The combined values from each detector will be given, each time they become available, to the SRS (Successive Running Sums) process. This process, discussed in Chapter 6, produces and maintains a number of histories, in the form of moving sum windows, for each detector.

Figure 2-11: Block diagram of processes running in the surface FPGA.

Those sums are compared with their corresponding threshold limits in the TC (Threshold Comparator) process every time they become updated. If one or more of them are found to be higher, a dump request is signalled. All dump requests are gathered initially by the Masking process, which serves the purpose of distinguishing between "Maskable" and "Not-Maskable" channels. The information necessary for the operation of the TC and the Masking processes, that is, the threshold and the masking values, are stored in tables uniquely created for each card. Those two processes together with their tables are discussed in Chapter 7.

Finally, for supervision and logging purposes, two more processes are created and are discussed in Chapter 8. The MaxValues process, which calculates and keeps the maximum values given in a period of time by each moving sum window, and the ESR process, which reports the errors found in the transmissions and the status of the tunnel electronics. Both of them are collected by the crate PowerPC and projected in the Control Room's displays.

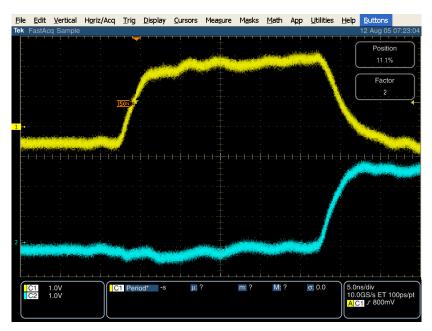

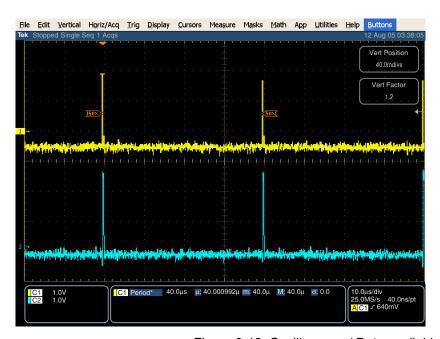

## 2.5 OUTPUT SIGNAL CONCENTRATION